Silicon Carbide Power MOSFET E-Series Automotive N-Channel Enhancement Mode

#### **Features**

- 3rd generation SiC MOSFET technology

- Optimized package with separate driver source pin

- 4.7mm of creepage distance between drain and source

- High blocking voltage with low on-resistance

- · High-speed switching with low capacitances

- Fast intrinsic diode with low reverse recovery (Q,,)

- Halogen free, RoHS compliant

- Automotive Qualified (AEC-Q101) and PPAP Capable

#### **Benefits**

- Reduce switching losses and minimize gate ringing

- Higher system efficiency

- · Reduce cooling requirements

- Increase power density

- · Increase system switching frequency

#### **Typical Applications**

- Motor Control

- EV Battery Chargers

- High Voltage DC/DC Converters

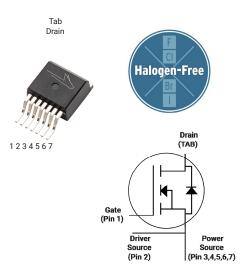

# Package

| Part Number  | Package    | Marking      |

|--------------|------------|--------------|

| E3M0021120J2 | T0-263-7XL | E3M0021120J2 |

#### **Maximum Ratings** ( $T_c = 25 \, ^{\circ}\text{C}$ unless otherwise specified)

| Symbol                     | Parameter                                                                     | Value                 | Unit   | Note               |         |

|----------------------------|-------------------------------------------------------------------------------|-----------------------|--------|--------------------|---------|

| $V_{DSmax}$                | Drain - Source Voltage                                                        |                       | 1200   | ٧                  |         |

| $V_{GSmax}$                | Gate - Source Voltage                                                         |                       | -8/+19 | ٧                  | Note: 1 |

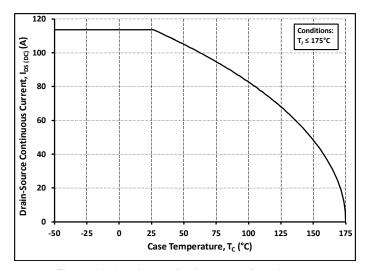

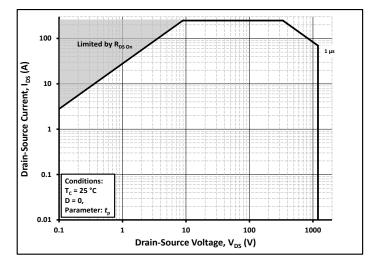

| I <sub>D</sub>             | 0 - i                                                                         | T <sub>C</sub> = 25°C | 114    | А                  | Fig. 19 |

|                            | Continuous Drain Current, V <sub>GS</sub> = 15 V $T_C = 100^{\circ}C$         |                       |        | A                  | Note: 2 |

| $I_{D(pulse)}$             | Pulsed Drain Current, Pulse width t <sub>P</sub> limited by T <sub>jmax</sub> | 248                   | А      | Fig. 22            |         |

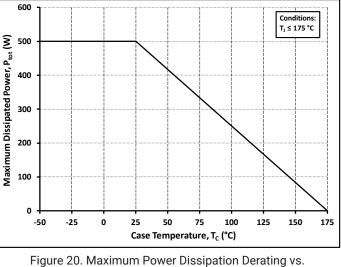

| $P_{\scriptscriptstyle D}$ | Power Dissipation, T <sub>c</sub> =25°C, T <sub>J</sub> = 175 °C              | 500                   | W      | Fig. 20<br>Note: 2 |         |

| $T_{J}$ , $T_{stg}$        | Operating Junction and Storage Temperature                                    |                       |        | °C                 |         |

| T <sub>L</sub>             | Solder Temperature, 1.6mm (0.063") from case for 10s                          | 260                   | °C     |                    |         |

Note (1): Recommended turn off / turn on gate voltage  $V_{\rm GS}$  - 4V...0V / +15V

Note (2): Verified by design

### **Electrical Characteristics** ( $T_c = 25^{\circ}C$ unless otherwise specified)

| Symbol               | Parameter                                     | Min. | Тур. | Max.     | Unit                                                 | Test Conditions                                                                                                                                  | Note           |

|----------------------|-----------------------------------------------|------|------|----------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| V <sub>(BR)DSS</sub> | Drain-Source Breakdown Voltage                | 1200 |      |          | V                                                    | V <sub>GS</sub> = 0 V, I <sub>D</sub> = 100 μA                                                                                                   |                |

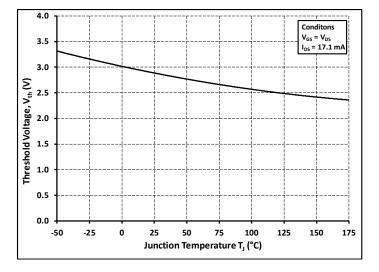

| V                    | Cata Thurshald Valtage                        | 1.8  | 2.9  | 3.8      | V                                                    | V <sub>DS</sub> = V <sub>GS</sub> , I <sub>D</sub> = 17.10 mA                                                                                    | Fig. 11        |

| $V_{GS(th)}$         | Gate Threshold Voltage                        |      | 2.3  |          | V                                                    | $V_{DS} = V_{GS}$ , $I_D = 17.10$ mA, $T_J = 175$ °C                                                                                             | Fig. 11        |

| I <sub>DSS</sub>     | Zero Gate Voltage Drain Current               |      | 1    | 50       | μΑ                                                   | V <sub>DS</sub> = 1200 V, V <sub>GS</sub> = 0 V                                                                                                  |                |

| I <sub>GSS</sub>     | Gate-Source Leakage Current                   |      | 10   | 250      | nA                                                   | V <sub>GS</sub> = 15 V, V <sub>DS</sub> = 0 V                                                                                                    |                |

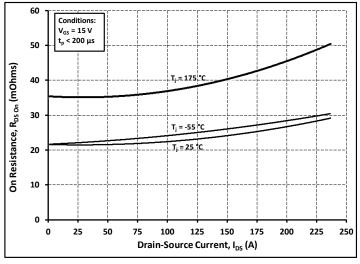

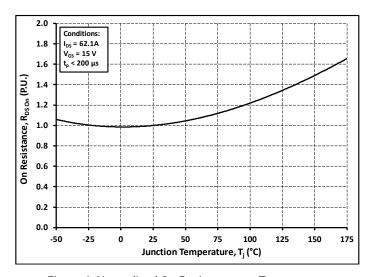

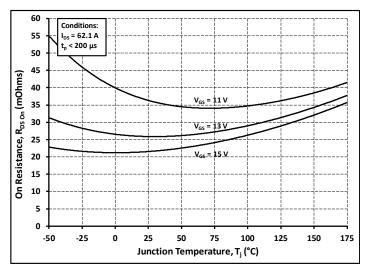

| R <sub>DS(on)</sub>  | Drain-Source On-State Resistance              |      | 21   | 29       | mΩ                                                   | V <sub>GS</sub> = 15 V, I <sub>D</sub> = 62.12 A                                                                                                 | Fig. 4,        |

| US(on)               | Drain Godice on State Resistance              |      | 35   |          | 11152                                                | $V_{GS} = 15 \text{ V}, I_D = 62.12 \text{ A}, T_J = 175^{\circ}\text{C}$                                                                        | 5, 6           |

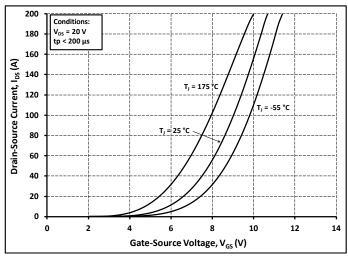

|                      | Transconductance                              |      | 38   |          | s                                                    | V <sub>DS</sub> = 20 V, I <sub>DS</sub> = 62.12 A                                                                                                | Fig. 7         |

| 915                  | Transconductance                              |      | 35   | <u> </u> | Ŭ                                                    | V <sub>DS</sub> = 20 V, I <sub>DS</sub> = 62.12 A, T <sub>J</sub> = 175°C                                                                        | 1 19. 7        |

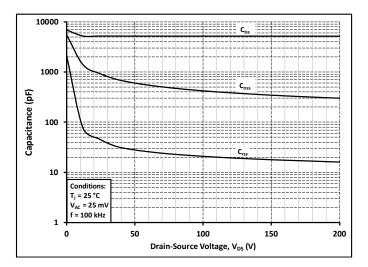

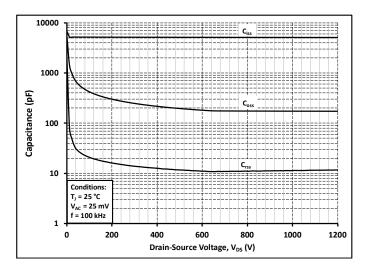

| C <sub>iss</sub>     | Input Capacitance                             |      | 5100 |          |                                                      | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 0V to 1000 V                                                                                            |                |

| Coss                 | Output Capacitance                            |      | 174  |          | pF                                                   | f = 100 kHz                                                                                                                                      | Fig. 17,<br>18 |

| C <sub>rss</sub>     | Reverse Transfer Capacitance                  |      | 11   |          | ]                                                    | V <sub>AC</sub> = 25 mV                                                                                                                          |                |

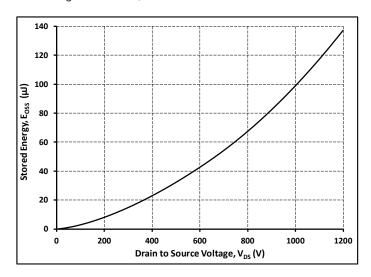

| Eoss                 | Coss Stored Energy                            |      | 98   |          | μJ                                                   | V <sub>DS</sub> = 800 V, f = 100 kHz                                                                                                             | Fig. 16        |

| C <sub>o(er)</sub>   | Effective Output Capacitance (Energy Related) |      | 210  |          | pF                                                   | V 0VV 0: 000V                                                                                                                                    |                |

| C <sub>o(tr)</sub>   | Effective Output Capacitance (Time Related)   |      | 323  |          | pF                                                   | $V_{GS} = 0 \text{ V, } V_{DS} = 0 \text{ to } 800 \text{V}$                                                                                     | Note: 3        |

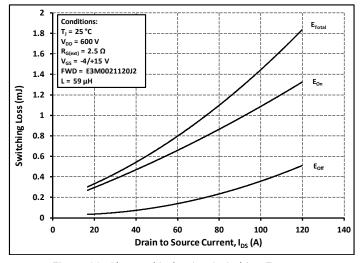

| Eon                  | Turn-On Switching Energy (Body Diode FWD)     |      | 1.7  |          |                                                      | V <sub>DS</sub> = 800 V, V <sub>GS</sub> = -4 V/15 V, I <sub>D</sub> = 62.12 A,                                                                  | Fig. 26,       |

| E <sub>OFF</sub>     | Turn-Off Switching Energy (Body Diode FWD)    |      | 0.3  |          | mJ                                                   | $R_{G(ext)}$ = 2.5 Ω, L= 59 μH, $T_J$ = 175°C<br>FWD = Internal Body Diode                                                                       | 28             |

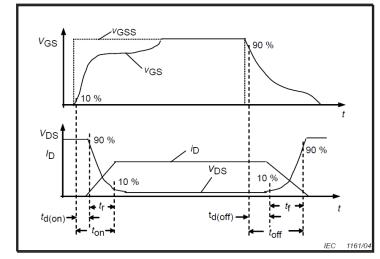

| t <sub>d(on)</sub>   | Turn-On Delay Time                            |      | 15   |          |                                                      |                                                                                                                                                  |                |

| t <sub>r</sub>       | Rise Time                                     |      | 34   |          | ]                                                    | $V_{DD}$ = 800 V, $V_{GS}$ = -4 V/15 V, $I_D$ = 62.12 A, $R_{G(ext)}$ = 2.5 Ω, L= 59 μH, $T_J$ = 25°C Timing relative to $V_{DS}$ Inductive load | Fig. 27,       |

| t <sub>d(off)</sub>  | Turn-Off Delay Time                           |      | 54   |          | ns                                                   |                                                                                                                                                  | 28             |

| t <sub>f</sub>       | Fall Time                                     |      | 13   |          |                                                      | inductive load                                                                                                                                   |                |

| R <sub>G(int)</sub>  | Internal Gate Resistance                      |      | 2.9  |          | Ω                                                    | f = 1 MHz                                                                                                                                        |                |

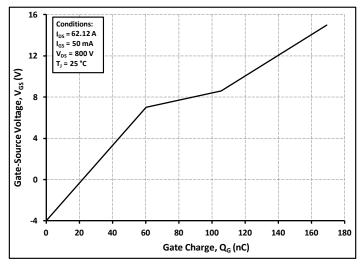

| $Q_{gs}$             | Gate to Source Charge                         |      | 60   |          | V <sub>DS</sub> = 800 V, V <sub>GS</sub> = -4 V/15 \ |                                                                                                                                                  |                |

| $Q_{gd}$             | Gate to Drain Charge                          |      | 45   | ]        | nC                                                   | I <sub>D</sub> = 62.12 A                                                                                                                         | Fig. 12        |

| Qg                   | Total Gate Charge                             |      | 169  |          |                                                      | Per IEC60747-8-4 pg 21                                                                                                                           |                |

Note (3):  $C_{o(er)}$ , a lumped capacitance that gives same stored energy as Coss while Vds is rising from 0 to 800V  $C_{o(tr)}$ , a lumped capacitance that gives same charging time as Coss while Vds is rising from 0 to 800V

## **Reverse Diode Characteristics** ( $T_c = 25^{\circ}C$ unless otherwise specified)

| Symbol                 | Parameter                        | Тур. | Max. | Unit | Test Conditions                                                                                                                                | Note    |

|------------------------|----------------------------------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| V                      | Die de Fermand Welteren          | 4.9  |      | V    | V <sub>GS</sub> = -4 V, I <sub>SD</sub> = 31.1 A, T <sub>J</sub> = 25 °C                                                                       | Fig. 8, |

| V <sub>SD</sub>        | Diode Forward Voltage            | 4.4  |      | V    | V <sub>GS</sub> = -4 V, I <sub>SD</sub> = 31.1 A, T <sub>J</sub> = 175 °C                                                                      | 9,10    |

| Is                     | Continuous Diode Forward Current |      | 85   | Α    | V <sub>GS</sub> = -4 V, T <sub>C</sub> = 25°C                                                                                                  |         |

| I <sub>S</sub> , pulse | Diode pulse Current              |      | 248  | А    | $V_{GS}$ = -4 V, pulse width $t_P$ limited by $T_{jmax}$                                                                                       |         |

| t <sub>rr</sub>        | Reverse Recover time             | 16   |      | ns   |                                                                                                                                                |         |

| Q <sub>rr</sub>        | Reverse Recovery Charge          | 416  |      | nC   | $V_{GS} = -4 \text{ V, } I_{SD} = 62.12 \text{ A, } V_{R} = 800 \text{ V}$<br>$dI_{F}/dt = 5300 \text{ A/}\mu\text{s, } T_{J} = 25 \text{ °C}$ |         |

| I <sub>rrm</sub>       | Peak Reverse Recovery Current    | 44   |      | А    |                                                                                                                                                |         |

| t <sub>rr</sub>        | Reverse Recover time             | 22   |      | ns   |                                                                                                                                                |         |

| Q <sub>rr</sub>        | Reverse Recovery Charge          | 268  |      | nC   | V <sub>GS</sub> = -4 V, I <sub>SD</sub> = 62.12 A, V <sub>R</sub> = 800 V<br>di <sub>E</sub> /dt = 2240 A/µs, T <sub>I</sub> = 25 °C           |         |

| I <sub>rrm</sub>       | Peak Reverse Recovery Current    | 21   |      | А    | ], at ==, ps,                                                                                                                                  |         |

#### **Thermal Characteristics**

| Symbol          | Parameter                                | Тур. | Max. | Unit | Test Conditions | Note    |

|-----------------|------------------------------------------|------|------|------|-----------------|---------|

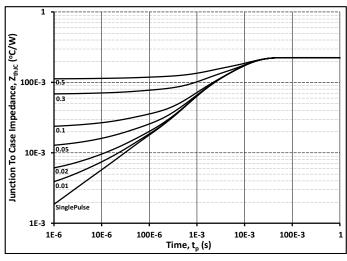

| $R_{\theta JC}$ | Thermal Resistance from Junction to Case | 0.23 | 0.30 | °C/W |                 | Fig. 21 |

## 4

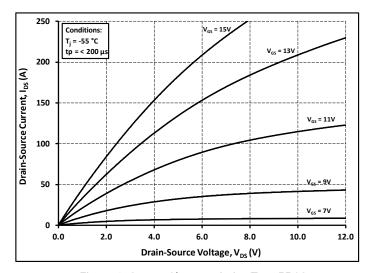

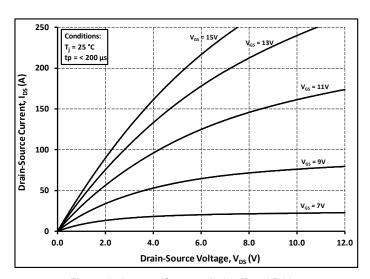

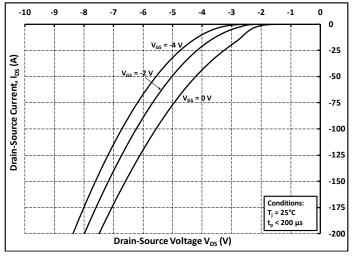

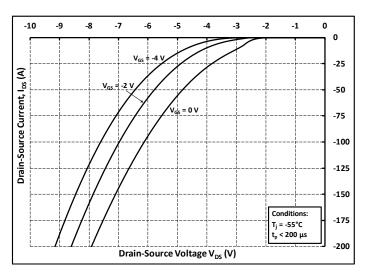

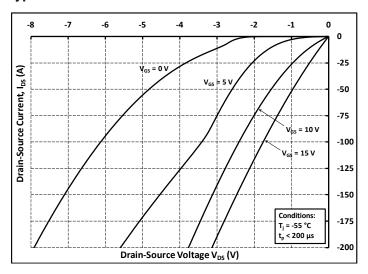

Figure 1. Output Characteristics T<sub>J</sub> = -55 °C

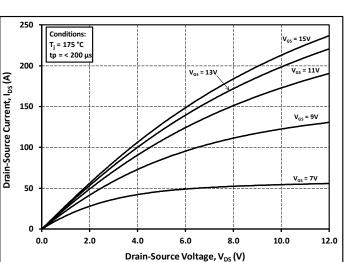

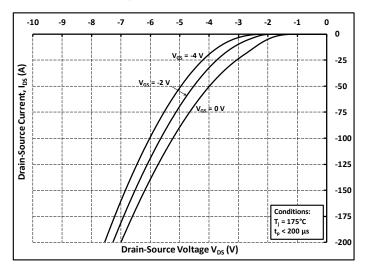

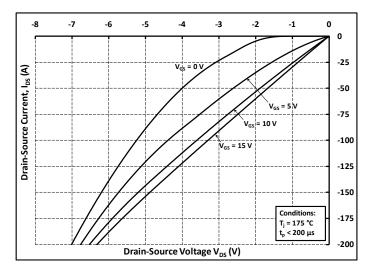

Figure 3. Output Characteristics T<sub>J</sub> = 175 °C

Figure 5. On-Resistance vs. Drain Current For Various Temperatures

Figure 2. Output Characteristics T<sub>J</sub> = 25 °C

Figure 4. Normalized On-Resistance vs. Temperature

Figure 6. On-Resistance vs. Temperature For Various Gate Voltage

Figure 7. Transfer Characteristic for Various Junction Temperatures

Figure 9. Body Diode Characteristic at 25 °C

Figure 11. Threshold Voltage vs. Temperature

Figure 8. Body Diode Characteristic at -55 °C

Figure 10. Body Diode Characteristic at 175 °C

Figure 12. Gate Charge Characteristics

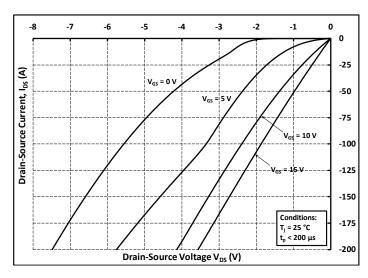

Figure 13. 3rd Quadrant Characteristic at -55 °C

Figure 15. 3rd Quadrant Characteristic at 175 °C

Figure 17. Capacitances vs. Drain-Source Voltage (0 - 200V)

Figure 14. 3rd Quadrant Characteristic at 25 °C

Figure 16. Output Capacitor Stored Energy

Figure 18. Capacitances vs. Drain-Source Voltage (0 - 1200V)

Figure 19. Continuous Drain Current Derating vs.

Case Temperature

Figure 20. Maximum Power Dissipation Derating vs Case Temperature

Figure 21. Transient Thermal Impedance (Junction - Case)

Figure 22. Safe Operating Area

Figure 23. Clamped Inductive Switching Energy vs. Drain Current ( $V_{DD} = 600V$ )

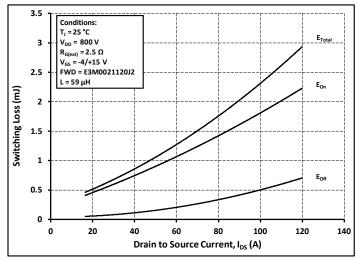

Figure 24. Clamped Inductive Switching Energy vs. Drain Current ( $V_{DD}$  = 800V)

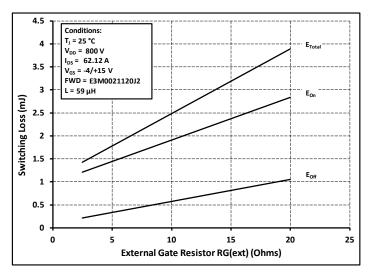

Figure 25. Clamped Inductive Switching Energy vs.  $R_{G(ext)}$

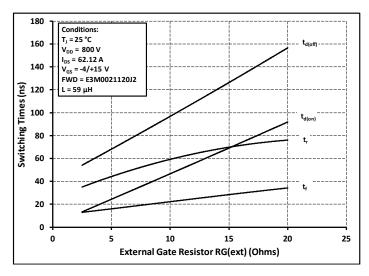

Figure 27. Switching Times vs.  $R_{G(ext)}$

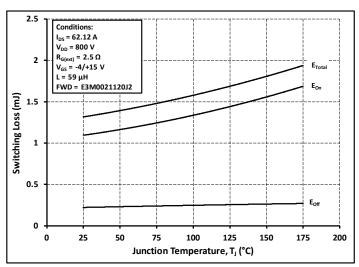

Figure 26. Clamped Inductive Switching Energy vs.

Temperature

Figure 28. Switching Times Definition

9

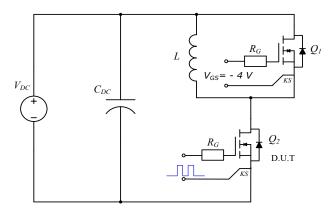

#### **Test Circuit Schematic**

Figure 29. Clamped Inductive Switching Waveform Test Circuit

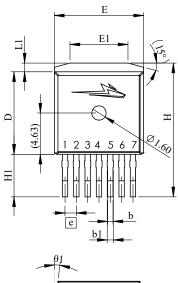

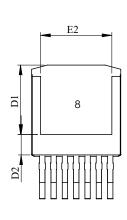

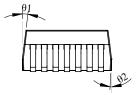

#### **Package Dimensions**

| SYMBOL | MIN (mm) | MAX (mm) |  |  |

|--------|----------|----------|--|--|

| A      | 4.30     | 4.70     |  |  |

| A1     | 0.00     | 0.25     |  |  |

| A2     | 2.20     | 2.60     |  |  |

| ь      | 0.52     | 0.72     |  |  |

| b1     | 0.60     | 0.80     |  |  |

| c      | 0.42     | 0.62     |  |  |

| c1     | 1.07     | 1.47     |  |  |

| D      | 9.05     | 9.45     |  |  |

| D1     | 7.58     | 7.98     |  |  |

| D2     | 2.05     | 2.45     |  |  |

| Е      | 9.80     | 10.20    |  |  |

| E1     | 6.30     | 6.97     |  |  |

| E2     | 7.80     | 8.20     |  |  |

| e      | 1.27 BSC |          |  |  |

| Н      | 14.87    | 15.27    |  |  |

| H1     | 4.55     | 4.95     |  |  |

| L      | 2.48     | 2.88     |  |  |

| L1     | 0.87     | 1.27     |  |  |

| θ      | 0°       | 8°       |  |  |

| θ1     | 4°       | 10°      |  |  |

| θ2     | 0°       | 6°       |  |  |

| 1 | GATE   |

|---|--------|

| 2 | KELVIN |

| 3 |        |

| 4 |        |

| 5 | SOURCE |

| 6 |        |

| 7 |        |

| 8 | DRAIN  |

#### NOTE

- 1. ALL METAL SURFACES ARE TIN PLATED (MATTE), EXCEPT AREA OF CUT.

- 2. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 3. ALL DIMENSIONS ARE LISTED IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 4. PACKAGE BURR FLASH SIZE (0.5 mm) IS NOT INCLUDED IN THE DIMENSIONS

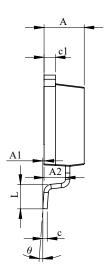

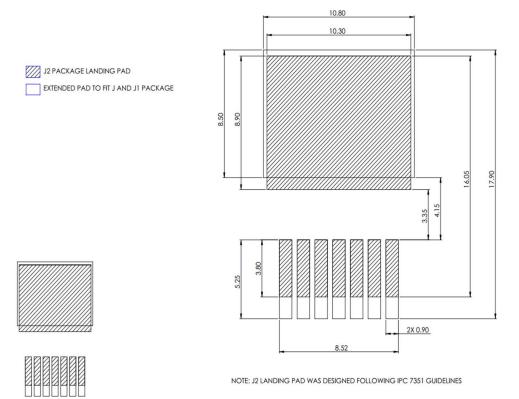

#### **Recommended Solder Pad Layout**

All dimensions in mm

#### **Revision history**

| Document Version | Date of release | Descriptiion of changes                                                           |

|------------------|-----------------|-----------------------------------------------------------------------------------|

| 1.0              | December 2023   | Initial release                                                                   |

| 2                | December- 2023  | Operating Temp Corrected                                                          |

| 3                | January - 2025  | Legal Disclaimer Updated                                                          |

| 4                | July - 2025     | V <sub>AC</sub> removed from R <sub>G(int)</sub> test condition<br>Fig 22 updated |

E3M0021120J2 1.

#### Notes & Disclaimer

WOLFSPEED PROVIDES TECHNICAL AND RELIABILITY DATA, DESIGN RESOURCES, APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, WITH RESPECT THERETO, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, SUITABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

This document and the information contained herein are subject to change without notice. Any such change shall be evidenced by the publication of an updated version of this document by Wolfspeed. No communication from any employee or agent of Wolfspeed or any third party shall effect an amendment or modification of this document. No responsibility is assumed by Wolfspeed for any infringement of patents or other rights of third parties which may result from use of the information contained herein. No license is granted by implication or otherwise under any patent or patent rights of Wolfspeed.

The information contained in this document (excluding examples, as well as figures or values that are labeled as "typical") constitutes Wolfspeed's sole published specifications for the subject product. "Typical" parameters are the average values expected by Wolfspeed in large quantities and are provided for informational purposes only. Any examples provided herein have not been produced under conditions intended to replicate any specific end use. Product performance can and does vary due to a number of factors.

This product has not been designed or tested for use in, and is not intended for use in, any application in which failure of the product would reasonably be expected to cause death, personal injury, or property damage. For purposes of (but without limiting) the foregoing, this product is not designed, intended, or authorized for use as a critical component in equipment implanted into the human body, life-support machines, cardiac defibrillators, and similar emergency medical equipment; air traffic control systems; or equipment used in the planning, construction, maintenance, or operation of nuclear facilities. Notwithstanding any application-specific information, guidance, assistance, or support that Wolfspeed may provide, the buyer of this product is solely responsible for determining the suitability of this product for the buyer's purposes, including without limitation (1) selecting the appropriate Wolfspeed products for the buyer's application, (2) designing, validating, and testing the buyer's application, and (3) ensuring the buyer's application meets applicable standards and any other legal, regulatory, and safety-related requirements.

#### **RoHS Compliance**

The levels of RoHS restricted materials in this product are below the maximum concentration values (also referred to as the threshold limits) permitted for such substances, or are used in an exempted application, in accordance with EU Directive 2011/65/EC (RoHS2), as implemented January 2, 2013. RoHS Declarations for this product can be obtained from your Wolfspeed representative or from the Product Documentation sections of www.wolfspeed. com.

#### **REACh Compliance**

REACh substances of high concern (SVHCs) information is available for this product. Since the European Chemical Agency (ECHA) has published notice of their intent to frequently revise the SVHC listing for the foreseeable future, please contact your Wolfspeed representative to ensure you get the most up-to-date REACh SVHC Declaration. REACh banned substance information (REACh Article 67) is also available upon request.

#### **Contact info:**

4600 Silicon Drive Durham, NC 27703 USA Tel: +1.919.313.5300 www.wolfspeed.com/power

© 2025 Wolfspeed, Inc. All rights reserved. Wolfspeed® and the Wolfstreak logo are registered trademarks and the Wolfspeed logo is a trademark of Wolfspeed, Inc. PATENT: https://www.wolfspeed.com/legal/patents

The information in this document is subject to change without notice.