# BF7006AMXX Series

BF7006AM64-LBTX

BF7006AM48-LBTX

BF7006AM28-TBBX

Datasheet

Rev1. 0

2021-05-18

Datasheet Page 1/161

# BF7006AMXX

# Content

| 1 | Chip Ov  | erview                                                  | 10 |

|---|----------|---------------------------------------------------------|----|

|   | 1.1      | System composition overview                             | 10 |

|   | 1.2      | The main resources of chip                              | 11 |

| 2 | Pins and | d Connections                                           | 13 |

|   | 2.1      | Device Pin Assignment                                   | 13 |

|   | 2.2      | Pin Availability by Package Pin-Count                   | 16 |

|   | 2.3      | Pin function description                                |    |

| 3 |          |                                                         |    |

| J | •        |                                                         |    |

|   | 3.1      | CPU                                                     |    |

|   | 3.2      | Address map                                             | 19 |

|   | 3.3      | System management                                       | 20 |

|   | 3.3.1    | Interrupt management                                    | 20 |

|   |          | 3.3.1.1 Interrupt allocation                            | 20 |

|   |          | 3.3.1.2 Interrupt enable and priority                   | 22 |

|   |          | 3.3.1.3 Interrupt wakeup                                | 22 |

|   |          | 3.3.1.4 Interrupt vector redirection and online upgrade | 22 |

|   | 3.3.2    | Reset management                                        | 24 |

|   |          | 3.3.2.1 Reset source                                    | 24 |

|   |          | 3.3.2.2 Reset filter                                    | 25 |

|   |          | 3.3.2.3 Reset sequence                                  | 26 |

|   | 3.3.3    | Clock and power consumption management                  | 26 |

|   |          | 3.3.3.1 Clock architecture                              | 27 |

|   |          | 3.3.3.2 Clock selection and switch                      | 28 |

|   |          | 3.3.3.3 Working modes                                   | 28 |

|   |          | 3.3.3.4 Low-power wakeup                                | 30 |

|   |          | 3.3.3.5 Oscillator clock initialization procedure       | 30 |

|   | 3.3.4    | Functional safety management                            | 31 |

|   |          | 3.3.4.1 External oscillator failure monitoring          | 31 |

|   |          | 3.3.4.2 Low-Voltage and power down monitoring           | 32 |

|   |          | 3.3.4.3 Memory protection and check                     | 32 |

|   |          | 3.3.4.4 Functional safety reset                         | 33 |

|   |          | 3.3.4.5 ADC temperature detection channel               | 33 |

|   | 3.3.5    | Register map                                            | 33 |

|   | 3.3.6 | Register description                |    |

|---|-------|-------------------------------------|----|

|   |       | 3.3.6.1 SYS_PTSEL register          | 34 |

|   |       | 3.3.6.2 SYS_XTAL_CTRL register      |    |

|   |       | 3.3.6.3 SYS_PLL_SOURCE_SEL register | 35 |

|   |       | 3.3.6.4 SYS_CLK_SEL register        |    |

|   |       | 3.3.6.5 SYS_VECTOR_OFFSET register  |    |

|   |       | 3.3.6.6 SYS_CLK_PD register         |    |

|   |       | 3.3.6.7 SYS_CAN_DOMAIN register     | 37 |

|   |       | 3.3.6.8 SYS_CLK_OUT register        | 37 |

|   |       | 3.3.6.9 SYS_IO_LOCK register        |    |

|   |       | 3.3.6.10 SYS_LVDT_CRL register      |    |

|   |       | 3.3.6.11 SYS_EXRST register         |    |

|   |       | 3.3.6.12 SYS_EXFLT register         |    |

|   |       | 3.3.6.13 SYS_PERH_HALT register     |    |

|   |       | 3.3.6.14 SYS_PLL_T register         |    |

|   |       | 3.3.6.15 SYS_CAN_CLKSEL register    |    |

|   |       | 3.3.6.16 SYS_CAN_RST register       |    |

|   |       | 3.3.6.17 SYS_CAN_SPWKFLAG register  |    |

|   |       | 3.3.6.18 SYS_RSTSTAT register       |    |

|   |       | 3.3.6.19 SYS_INTEN register         |    |

|   |       | 3.3.6.20 SYS_INTFLG register        |    |

|   |       | 3.3.6.21 SYS_XTAL_CHK register      |    |

|   |       | 3.3.6.22 SYS_XTAL_CHKCNT register   |    |

|   |       | 3.3.6.23 SYS_XTAL_INIT register     |    |

|   |       | 3.3.6.24 SYS_LVDT_IE register       |    |

|   |       | 3.3.6.25 SYS_LVDT_IF register       |    |

|   | 3.3.7 | Example program                     | 46 |

| 4 | Memor | ry                                  | 50 |

|   | 4.1   | FLASH                               | 50 |

|   | 4.1.1 | Features                            | 50 |

|   | 4.1.2 | FLASH_NVR                           | 50 |

|   | 4.2   | EEPROM                              | 50 |

|   | 4.2.1 | Features                            |    |

|   | 4.2.2 | EEPROM NVR                          |    |

|   |       | _                                   |    |

|   | 4.3   | SRAM                                |    |

|   | 4.4   | Register map                        | 51 |

|   | 4.5   | Register description                | 52 |

|   | 4.5.1 | EFLASH_SEL register                 | 52 |

|   | 4.5.2   | EFLASH_MODE register             | 52 |

|---|---------|----------------------------------|----|

|   | 4.5.3   | EFLASH_EBCFG register            | 52 |

|   | 4.5.4   | FLASH_STATE register             | 53 |

|   | 4.5.5   | EEPROM STATE register            | 53 |

|   | 4.5.6   | EFLASH_ECC_CTRL register         |    |

|   | 4.5.7   | EFLASH UNLOCK register           |    |

|   | 4.5.8   | FLASH LOCK SIZE register         |    |

|   |         |                                  |    |

|   | 4.5.9   | EEPROM_LOCK_SIZE register        |    |

| 5 | Periphe | erals                            | 55 |

| 4 | 5.1     | SCI                              | 55 |

|   | 5.1.1   | Features                         | 55 |

|   | 5.1.2   | Functional description           | 55 |

|   |         | 5.1.2.1 Baud rate generation     | 55 |

|   |         | 5.1.2.2 Transmitter function     |    |

|   |         | 5.1.2.3 Receiver function        | 57 |

|   |         | 5.1.2.4 Receiver sampling method | 58 |

|   |         | 5.1.2.5 Receiver wakeup          |    |

|   |         | 5.1.2.6 Pin connection modes     |    |

|   |         | 5.1.2.7 Interrupt wakeup         | 60 |

|   | 5.1.3   | Register map                     | 60 |

|   | 5.1.4   | Register description             | 61 |

|   |         | 5.1.4.1 SCI_BDH register         | 61 |

|   |         | 5.1.4.2 SCI_BDL register         | 61 |

|   |         | 5.1.4.3 SCI_C1 register          | 62 |

|   |         | 5.1.4.4 SCI_C2 register          | 63 |

|   |         | 5.1.4.5 SCI_S1 register          | 64 |

|   |         | 5.1.4.6 SCI_S2 register          | 66 |

|   |         | 5.1.4.7 SCI_C3 register          | 68 |

|   |         | 5.1.4.8 SCI_D register           | 69 |

|   |         | 5.1.4.9 SCI_EN register          | 69 |

|   | 5.1.5   | Example program                  | 69 |

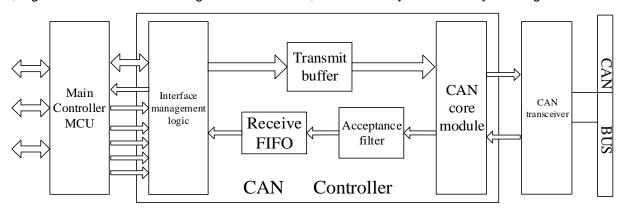

| 4 | 5.2     | CAN                              | 77 |

|   | 5.2.1   | Features                         | 77 |

|   | 5.2.2   | Functional description           | 78 |

|   |         | 5.2.2.1 FIFO                     | 78 |

|   |         |                                  |    |

|       | 5.2.2.2  | Receive buffer                                   | 79  |

|-------|----------|--------------------------------------------------|-----|

|       | 5.2.2.3  | Interrupt                                        | 79  |

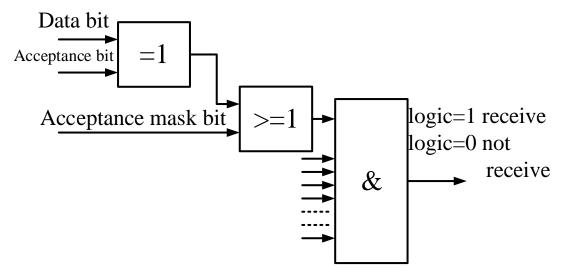

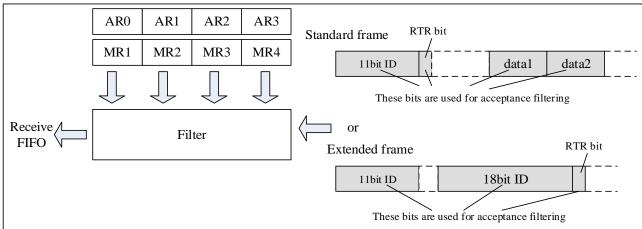

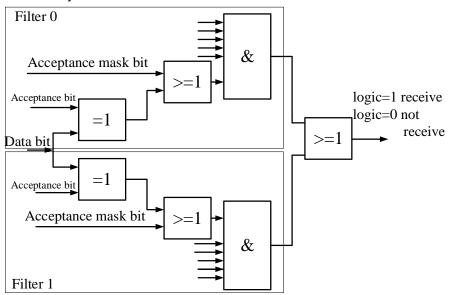

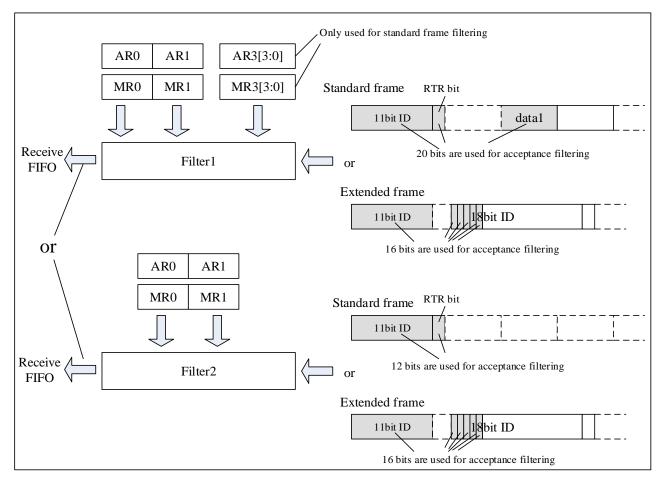

|       | 5.2.2.4  | Acceptance filtering                             | 80  |

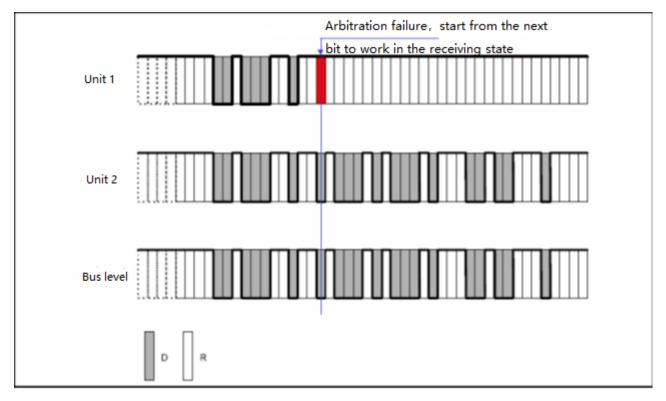

|       | 5.2.2.5  | Arbitration                                      | 85  |

|       | 5.2.2.6  | Loopback self test                               | 85  |

|       | 5.2.2.7  | CAN self wakeup                                  | 86  |

|       | 5.2.2.8  | CAN wakeup system                                | 86  |

| 5.2.3 | Register | map                                              | 87  |

| 5.2.4 | Register | description                                      | 88  |

|       | 5.2.4.1  | CAN_MOD register                                 | 88  |

|       | 5.2.4.2  | CAN_CMR register                                 | 89  |

|       | 5.2.4.3  | CAN_SR register                                  | 90  |

|       | 5.2.4.4  | CAN_IF register                                  | 92  |

|       | 5.2.4.5  | CAN_IE register                                  | 93  |

|       | 5.2.4.6  | CAN_BTR0 register                                | 94  |

|       | 5.2.4.7  | CAN_BTR1 register                                | 94  |

|       | 5.2.4.8  | CAN_SLPAK register                               | 95  |

|       | 5.2.4.9  | CAN_WUP register                                 | 95  |

|       | 5.2.4.10 | CAN_ALC register                                 | 96  |

|       | 5.2.4.11 | CAN_ECC register                                 | 98  |

|       | 5.2.4.12 | CAN_EMLR register                                | 99  |

|       | 5.2.4.13 | CAN_RXERR register                               | 99  |

|       | 5.2.4.14 | CAN_TXERR register                               | 100 |

|       | 5.2.4.15 | CAN_IDAR0/CAN_IDAR1/CAN_IDAR2/CAN_IDAR3 register | 100 |

|       |          | CAN_IDMR0/CAN_IDMR1/CAN_IDMR2/CAN_IDMR3 register |     |

|       | 5.2.4.17 | CAN_RMC register                                 | 101 |

|       | 5.2.4.18 | CAN_ENABLE register                              | 101 |

|       | 5.2.4.19 | CAN_CLRISR register                              | 101 |

|       | 5.2.4.20 | CAN_CLRECC register                              | 102 |

|       | 5.2.4.21 | CAN_FRCTL register                               | 102 |

|       | 5.2.4.22 | CAN_ID0/CAN_ID1/CAN_ID2/CAN_ID3 register         | 103 |

|       |          | CAN_DATA0~ CAN_DATA7 register                    |     |

|       | 5.2.4.24 | CAN_SWU_FILT register                            | 104 |

| 5.2.5 | Example  | program                                          | 104 |

| 5.3   | PWM      |                                                  | 108 |

| 5.3.1 | Features | 5                                                | 108 |

| 5.3.2 | Function | nal description                                  | 108 |

|       | 5.3.2.1  | Counter mode                                     | 108 |

|       | 5.3.2.2  | Input capture                                    | 109 |

|       | 5.3.2.3  | Output compare                                   | 109 |

|       | 5.3.2.4  | Edge aligned                                     | 110 |

|       |          |                                                  |     |

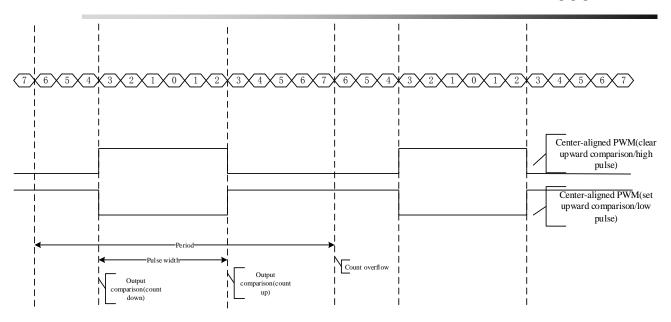

|       | 5.3.2.5 Center aligned            |     |

|-------|-----------------------------------|-----|

| 5.3.3 | Register map                      | 112 |

| 5.3.4 | Register description              | 113 |

|       | 5.3.4.1 PWM_SC register           |     |

|       | 5.3.4.2 PWM_CNT register          |     |

|       | 5.3.4.3 PWM_MOD register          |     |

|       | 5.3.4.4 PWM_CxSC (x=0~5) register |     |

|       | 5.3.4.5 PWM_CxV (x=0~5) register  |     |

| 5.3.5 | 5.3.4.6 PWM_ADCV register         |     |

|       | Example program                   |     |

| 5.4   | TIMER                             | 118 |

| 5.4.1 | Features                          | 118 |

| 5.4.2 | Functional description            | 118 |

| 5.4.3 | Register map                      | 118 |

| 5.4.4 | Register description              | 118 |

|       | 5.4.4.1 TIMER_CFG register        | 118 |

|       | 5.4.4.2 TIMER_MOD register        | 120 |

|       | 5.4.4.3 TIMER_CNT register        | 120 |

| 5.4.5 | Example program                   | 120 |

| 5.5   | RTC                               | 122 |

| 5.5.1 | Features                          | 122 |

| 5.5.2 | Functional description            | 122 |

|       | 5.5.2.1 General description       | 122 |

|       | 5.5.2.2 Frame wakeup              | 122 |

| 5.5.3 | Register map                      | 122 |

| 5.5.4 | Register description              | 123 |

|       | 5.5.4.1 RTC_SC register           |     |

|       | 5.5.4.2 RTC_CNT register          |     |

|       | 5.5.4.3 RTC_MOD register          | 124 |

| 5.5.5 | Example program                   | 124 |

| 5.6   | WDT                               | 125 |

| 5.6.1 | Features                          | 125 |

| 5.6.2 | Functional description            | 126 |

|       | 5.6.2.1 General description       | 126 |

|       | 5.6.2.2 Window mode               | 126 |

# BF7006AMXX

|       | 5.6.2.3  | WDT configuration protection | 126 |

|-------|----------|------------------------------|-----|

|       | 5.6.2.4  | Low-power wakeup             | 127 |

|       | 5.6.2.5  | Debug mode                   |     |

| 5.6.3 | Registe  | r map                        | 127 |

| 5.6.4 | Registe  | r description                |     |

|       | 5.6.4.1  | WDT_CS register              |     |

|       | 5.6.4.2  | WDT_CNT register             |     |

|       | 5.6.4.3  | WDT_TOVAL register           |     |

|       | 5.6.4.4  | WDT_WINVAL register          |     |

| 5.6.5 | Example  | e program                    | 129 |

| 5.7   | GPIO     |                              | 131 |

| 5.7.1 | Feature  | es                           | 131 |

| 5.7.2 | Function | nal description              | 131 |

|       | 5.7.2.1  | General description          |     |

|       | 5.7.2.2  | NMI interrupt                |     |

| 5.7.3 | Registe  | r map                        |     |

| 5.7.4 | Registe  | r description                | 133 |

|       | 5.7.4.1  | GPIO_PTDD (GPIOx) register   |     |

|       | 5.7.4.2  | GPIO_PTD (GPIOx) register    |     |

|       | 5.7.4.3  | GPIO_PTPE (GPIOx) register   |     |

|       | 5.7.4.4  | GPIO_PTSC (GPIOx) register   |     |

|       | 5.7.4.5  | GPIO_PTPS (GPIOx) register   |     |

|       | 5.7.4.6  | GPIO_PTES (GPIOx) register   |     |

|       | 5.7.4.7  | GPIO_INTST (GPIOx) register  |     |

|       | 5.7.4.8  | GPIO_NMISC register          |     |

| 5.7.5 | Example  | e program                    | 136 |

| 5.8   | ADC      |                              |     |

| 5.8.1 | Feature  | 25                           | 139 |

| 5.8.2 | Function | nal description              | 139 |

|       | 5.8.2.1  | General description          | 139 |

|       | 5.8.2.2  | Channnel selection           | 140 |

|       | 5.8.2.3  | Trigger methods              |     |

|       | 5.8.2.4  | ADC conversion               |     |

|       | 5.8.2.5  | Automatic compare            |     |

|       | 5.8.2.6  | Sleep wakeup                 | 142 |

|       | 5.8.2.7  | Time sequence description    | 142 |

|       | 5.8.2.8  | Self test function           | 143 |

| 5.8.3 | Registe  | r map                        | 144 |

|    | 5.8.4     | Register description                        | 144 |

|----|-----------|---------------------------------------------|-----|

|    |           | 5.8.4.1 ADC_SC1 register                    | 144 |

|    |           | 5.8.4.2 ADC_SC2 register                    | 145 |

|    |           | 5.8.4.3 ADC_DATA register                   | 146 |

|    |           | 5.8.4.4 ADC_CV0 register                    | 146 |

|    |           | 5.8.4.5 ADC_CV1 register                    | 146 |

|    |           | 5.8.4.6 ADC_CFG register                    | 147 |

|    |           | 5.8.4.7 ADC_APCTL register                  |     |

|    |           | 5.8.4.8 ADC_SPT register                    |     |

|    |           | 5.8.4.9 ADC_CKC register                    |     |

|    |           | 5.8.4.10 ADC_PD register                    |     |

|    |           | 5.8.4.11 ADC_TEST register                  |     |

|    |           | 5.8.4.12 ADC_IWK register                   |     |

|    | 5.8.5     | ADC reference application process           | 149 |

| 6  | Electrica | al characteristics                          | 150 |

| 6  | .1        | Thermal Characteristics                     | 150 |

| 6  | .2        | Moisture sensitivity index                  | 150 |

| 6  | .3        | ESD index                                   | 150 |

| 6  | .4        | Power Characteristics                       | 150 |

| 6  | .5        | Input and Output                            | 151 |

| 6  | .6        | Power-on, power-down, low-voltage detection | 151 |

| 6  | .7        | Clock source                                |     |

|    | .8        | Analog-to-Digital converter ADC             |     |

|    | .9        | Supply Current Characteristics              |     |

| 7  |           |                                             |     |

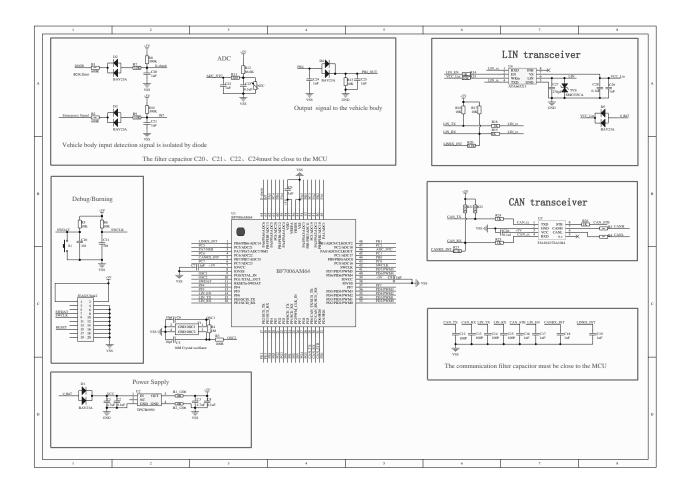

|    |           | nended reference applications               |     |

| 8  | Append    | ix A                                        | 155 |

| 9  | Append    | ix B                                        | 156 |

| 10 | Package   | 2                                           | 157 |

| 1  | 0.1       | Mechanical drawings                         | 157 |

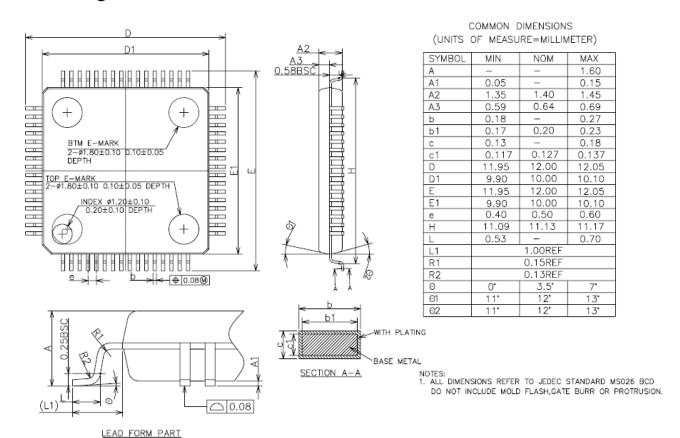

|    | 10.1.1    | LQFP64                                      | 157 |

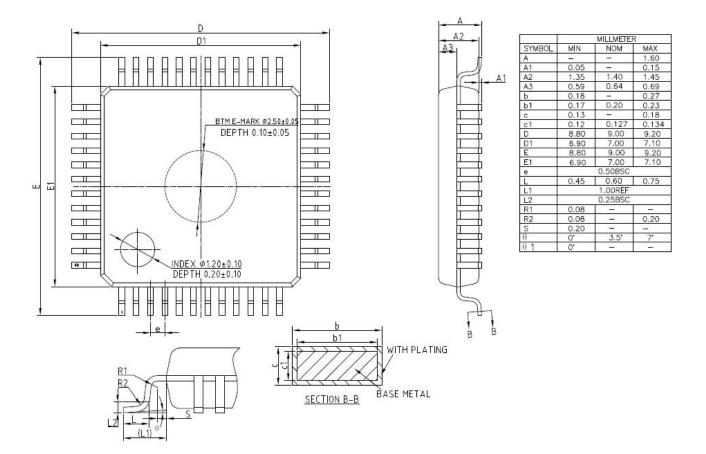

|    | 10.1.2    | LQFP48                                      | 158 |

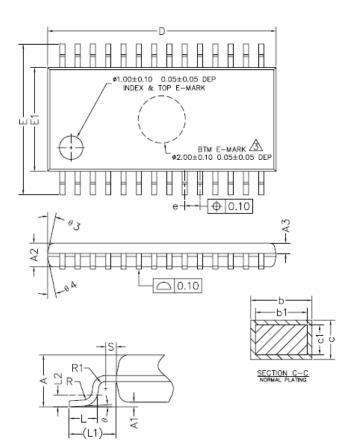

|    | 10.1.3    | TSSOP28                                     | 159 |

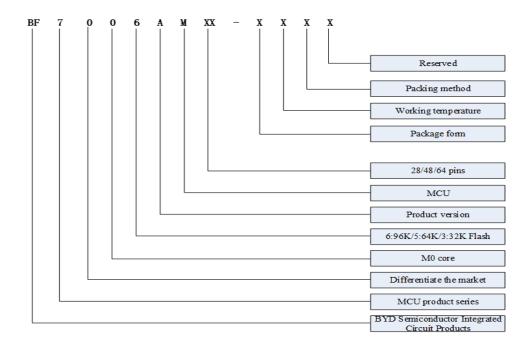

| 11 | Order ir  | nformation                                  | 160 |

Datasheet Page 9 / 163

# 1 Chip Overview

BF7006AMxx is a 32-bit general-purpose MCU that conform the automotive AECQ100 GRADE1 quality level. It is designed in according to the ISO26262 ASIL-B level standard. Besides, it integrates various communication modules such as CAN, LIN, UART, Multiple counter, Timer, and PWM functions, and contains a variety of general-purpose modules such as high-precision ADC, EEPROM instant data storage. The package form contains: LQFP64, LQFP48, TSSOP28. And these chips are suitable for a variety of automotive electronic body controls such as Electric window control, Electric seat control, Wipers, LED lamps, Door locks, etc.

# 1.1 System composition overview

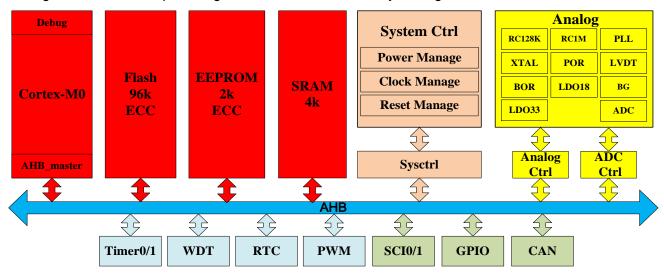

BF7006AMXX chip system composition is as follows:

| BF7006AMxx                               |                                   |                       |  |  |  |  |  |

|------------------------------------------|-----------------------------------|-----------------------|--|--|--|--|--|

| System Control                           | CORE                              | Analog System         |  |  |  |  |  |

| Power Manage  Clock Manage  Reset Manage | ARM Cortex-M0  Flash EEPROM  SRAM | LDO18  LDO33  BG  POR |  |  |  |  |  |

| Communication SCI                        | Timers WDT                        | BOR LVDT ADC RC128K   |  |  |  |  |  |

| CAN GPIO                                 | Timer0、Timer1  PWM                | XOSC PLL              |  |  |  |  |  |

Datasheet Page 10 of 161

# 1.2 The main resources of chip

The main resources of the BF7006AMXX chip are as follows ,and the specific module functions are described in the chapters of each module:

| Category   | Features                       | LQFP64                    | LQFP48                    | TSSOP28                    |

|------------|--------------------------------|---------------------------|---------------------------|----------------------------|

|            | CPU                            | Cortex_M0                 | Cortex_M0                 | Cortex_M0                  |

|            | Frequency                      | MAX:32MHz                 | MAX:32MHz                 | MAX:32MHz                  |

| System     | EX INT                         | MAX:24 channels           | MAX:24 channels           | MAX:14 channels            |

|            | Ю                              | MAX:54 channels           | MAX:40 channels           | MAX:22 channels            |

|            | High current driver IO         | MAX:6 channels            | MAX:6 channels            | MAX:6 channels             |

| 01 1       |                                | RC1MHz、RC128KHz、          | RC1MHz、RC128KHz、          | RC1MHz、RC128KHz、           |

| Clock      | Internal                       | PLL                       | PLL                       | PLL                        |

| Source     | External                       | XTAL 8MHz/16MHz           | XTAL 8MHz/16MHz           | XTAL 8MHz/16MHz            |

|            | FLASH                          | MAX:96KB                  | MAX:96KB                  | MAX:96KB                   |

| Memory     | EEPROM                         | MAX:2KB                   | MAX:2KB                   | MAX:2KB                    |

|            | SRAM                           | MAX:4KB                   | MAX:4KB                   | MAX:4KB                    |

| Commun     | CAN                            | MAX:1                     | MAX:1                     | MAX:1                      |

| ication    | SCI                            |                           |                           | MAX:2                      |

|            | System Timer                   | 1 of CPU internal         | 1 of CPU internal         | 1 of CPU internal          |

| 0 , ,      | RTC                            | MAX:1, 32-bit RTC         | MAX:1, 32-bit RTC         | MAX:1, 32-bit RTC          |

| Counter/   | Timer                          | MAX:2, 16-bit timers      | MAX:2, 16-bit timers      | MAX:2, 16-bit timers       |

| Timer      | D) A (A A                      | MAX:6 channels, 16-bit    | MAX:6 channels, 16-bit    | MAX:6 channels, 16-bit     |

|            | PWM                            | pwm                       | pwm                       | pwm                        |

|            |                                | Max:24 channels, Max:12-  | Max:16 channels, Max:12-  | Max:8 channels, Max:12-bit |

| A I:       | 400                            | bit resolution,Max:10-bit | bit resolution,Max:10-bit | resolution,Max:10-bit      |

| Analog     | ADC                            | accuracy, Max:1M          | accuracy, Max:1M          | accuracy, Max:1M           |

|            |                                | sampling rate             | sampling rate             | sampling rate              |

|            | Debug interface                | ARM Serial Wire           | ARM Serial Wire           | ARM Serial Wire            |

| Debug      | Number of hardware breakpoints | Max:2                     | Max:2                     | Max:2                      |

|            | Low voltage detection          | 3 levels                  | 3 levels                  | 3 levels                   |

|            | Power-down reset               | support                   | support                   | support                    |

|            | ECC verification               | 6-bit ECC,FLASH、          | 6-bit ECC,FLASH、          | 6-bit ECC,FLASH、           |

|            | ECC verification               | EEPROM                    | EEPROM                    | EEPROM                     |

| Function   | Memory protection              | FLASH、EEPROM              | FLASH、EEPROM              | FLASH、EEPROM               |

|            | CPU crash monitoring           | Supports CPU crash reset  | Supports CPU crash reset  | Supports CPU crash reset   |

| Safety     | Clask assumb                   | Supports external crystal | Supports external crystal | Supports external crystal  |

|            | Clock security                 | oscillator failure reset  | oscillator failure reset  | oscillator failure reset   |

|            | Hardware WDT                   | Supports WDT reset        | Supports WDT reset        | Supports WDT reset         |

|            | Module power-on self-          | CAN                       | CAN                       | CAN                        |

|            | check                          | CAN                       | CAN                       | CAN                        |

| Main       | Operating Voltage              | 3.3V~5.5V                 | 3.3V~5.5V                 | 3.3V~5.5V                  |

| electrical | Operating Temperature          | -40°C~+125°C              | -40°C~+125°C              | -40°C~+125°C               |

Datasheet Page 11 of 161

## BF7006AMXX

| Category | Features         | LQFP64       | LQFP48       | TSSOP28      |

|----------|------------------|--------------|--------------|--------------|

| characte | ESD feature      | HBM: ≥6kv    | HBM: ≥6kv    | HBM: ≥6kv    |

| ristics  | ESD leature      | CDM: ≥0.5kv  | CDM: ≥0.5kv  | CDM: ≥0.5kv  |

|          | Latch up feature | 100mA (25°C) | 100mA (25°C) | 100mA (25°C) |

Datasheet Page 12 of 161

# 2 Pins and Connections

This section describes the package forms of the BF7006AMXX series and the schematic diagram of the pins. The detailed description of the function of all pins, and the function multiplexing of each pin.

## 2.1 Device Pin Assignment

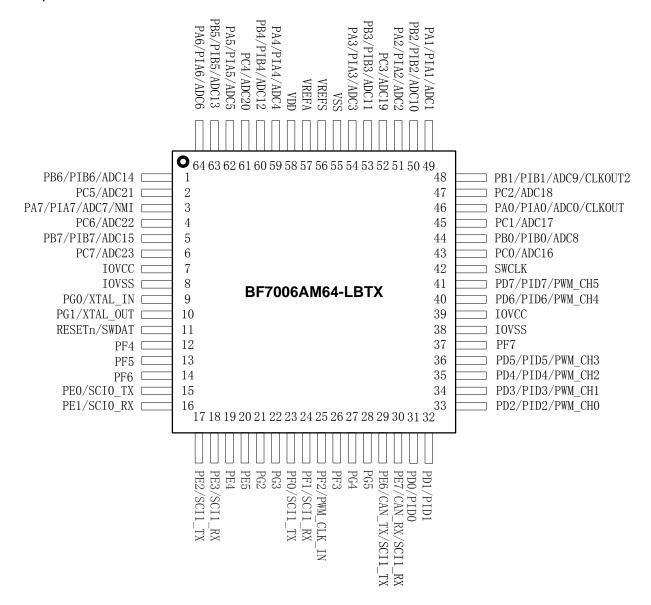

This section shows the pin assignments for BF7006AMXX Series MCUs in the available packages. 64-pin LQFP64:

Datasheet Page 13 of 161

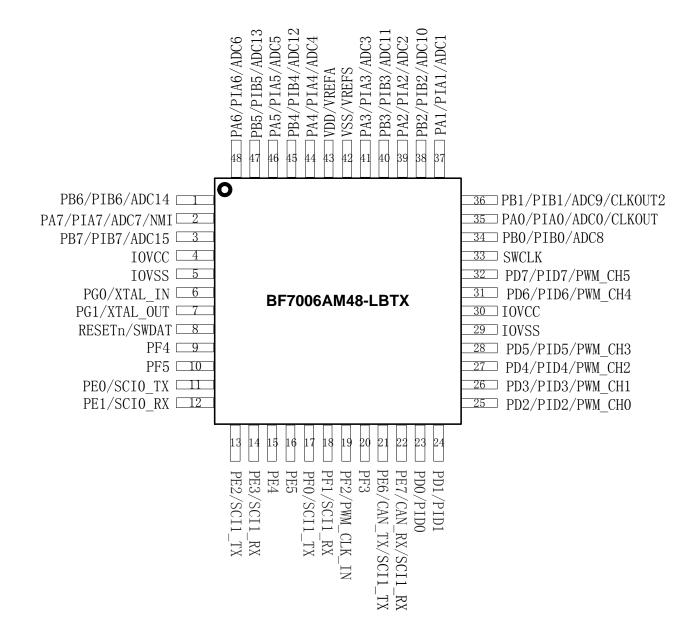

48-pin LQFP48:

Datasheet Page 14 of 161

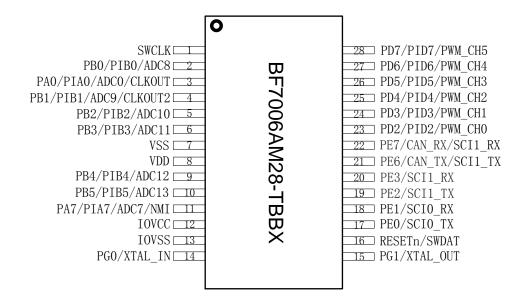

28-pin TSSOP28:

Datasheet Page 15 of 161

# 2.2 Pin Availability by Package Pin-Count

|        |        |       | Lowest   | ← Priority | v → Highest |          |           |          |

|--------|--------|-------|----------|------------|-------------|----------|-----------|----------|

| LOFDCA | LOED40 | TSSOP | First    | Second     | Third       | Forth    | Fifth     | Sixth    |

| LQFP64 | LQFP48 | 28    | function | function   | function    | function | function  | function |

| 1      | 1      |       | PB6      | PIB6       | ADC14       |          |           |          |

| 2      |        |       | PC5      |            | ADC21       |          |           |          |

| 3      | 2      | 11    | PA7      | PIA7       | ADC7        |          | NMI       |          |

| 4      |        |       | PC6      |            | ADC22       |          |           |          |

| 5      | 3      |       | PB7      | PIB7       | ADC15       |          |           |          |

| 6      |        |       | PC7      |            | ADC23       |          |           |          |

| 7      | 4      | 12    |          |            |             |          |           | IOVCC    |

| 8      | 5      | 13    |          |            |             |          |           | IOVSS    |

| 9      | 6      | 14    | PG0      |            |             |          | XTAL_IN   |          |

| 10     | 7      | 15    | PG1      |            |             |          | XTAL_OUT  |          |

| 11     | 8      | 16    |          |            |             | SWDAT    | RESETn    |          |

| 12     | 9      |       | PF4      |            |             |          |           |          |

| 13     | 10     |       | PF5      |            |             |          |           |          |

| 14     |        |       | PF6      |            |             |          |           |          |

| 15     | 11     | 17    | PE0      |            |             |          | SCI0_TX   |          |

| 16     | 12     | 18    | PE1      |            |             |          | SCI0_RX   |          |

| 17     | 13     | 19    | PE2      |            |             |          | SCI1_TX   |          |

| 18     | 14     | 20    | PE3      |            |             |          | SCI1_RX   |          |

| 19     | 15     |       | PE4      |            |             |          |           |          |

| 20     | 16     |       | PE5      |            |             |          |           |          |

| 21     |        |       | PG2      |            |             |          |           |          |

| 22     |        |       | PG3      |            |             |          |           |          |

| 23     | 17     |       | PF0      |            |             |          | SCI1_TX   |          |

| 24     | 18     |       | PF1      |            |             |          | SCI1_RX   |          |

|        |        |       |          |            |             |          | PWM_CLK_I |          |

| 25     | 19     |       | PF2      |            |             |          | N         |          |

| 26     | 20     |       | PF3      |            |             |          |           |          |

| 27     |        |       | PG4      |            |             |          |           |          |

| 28     |        |       | PG5      |            |             |          |           |          |

| 29     | 21     | 21    | PE6      |            |             | SCI1_TX  | CAN_TX    |          |

| 30     | 22     | 22    | PE7      |            |             | SCI1_RX  | CAN_RX    |          |

| 31     | 23     |       | PD0      | PID0       |             |          |           |          |

| 32     | 24     |       | PD1      | PID1       |             |          |           |          |

| 33     | 25     | 23    | PD2      | PID2       |             |          | PWM_CH0   |          |

| 34     | 26     | 24    | PD3      | PID3       |             |          | PWM_CH1   |          |

| 35     | 27     | 25    | PD4      | PID4       |             |          | PWM_CH2   |          |

| 36     | 28     | 26    | PD5      | PID5       |             |          | PWM_CH3   |          |

Datasheet Page 16 of 161

|        | Lowest ← Priority → Highest |       |          |          |          |          |          |          |

|--------|-----------------------------|-------|----------|----------|----------|----------|----------|----------|

| LOFDOA | 1.05040                     | TSSOP | First    | Second   | Third    | Forth    | Fifth    | Sixth    |

| LQFP64 | LQFP48                      | 28    | function | function | function | function | function | function |

| 37     |                             |       | PF7      |          |          |          |          |          |

| 38     | 29                          |       |          |          |          |          |          | IOVSS    |

| 39     | 30                          |       |          |          |          |          |          | IOVCC    |

| 40     | 31                          | 27    | PD6      | PID6     |          |          | PWM_CH4  |          |

| 41     | 32                          | 28    | PD7      | PID7     |          |          | PWM_CH5  |          |

| 42     | 33                          | 1     |          |          |          |          | SWCLK    |          |

| 43     |                             |       | PC0      |          | ADC16    |          |          |          |

| 44     | 34                          | 2     | PB0      | PIB0     | ADC8     |          |          |          |

| 45     |                             |       | PC1      |          | ADC17    |          |          |          |

| 46     | 35                          | 3     | PA0      | PIA0     | ADC0     |          | CLKOUT   |          |

| 47     |                             |       | PC2      |          | ADC18    |          |          |          |

| 48     | 36                          | 4     | PB1      | PIB1     | ADC9     |          | CLKOUT2  |          |

| 49     | 37                          |       | PA1      | PIA1     | ADC1     |          |          |          |

| 50     | 38                          | 5     | PB2      | PIB2     | ADC10    |          |          |          |

| 51     | 39                          |       | PA2      | PIA2     | ADC2     |          |          |          |

| 52     |                             |       | PC3      |          | ADC19    |          |          |          |

| 53     | 40                          | 6     | PB3      | PIB3     | ADC11    |          |          |          |

| 54     | 41                          |       | PA3      | PIA3     | ADC3     |          |          |          |

| 55     | 42                          | 7     |          |          |          |          |          | VSS      |

| 56     |                             |       |          |          |          |          |          | VREFS    |

| 57     |                             |       |          |          |          |          |          | VREFA    |

| 58     | 43                          | 8     |          |          |          |          |          | VDD      |

| 59     | 44                          |       | PA4      | PIA4     | ADC4     |          |          |          |

| 60     | 45                          | 9     | PB4      | PIB4     | ADC12    |          |          |          |

| 61     |                             |       | PC4      |          | ADC20    |          |          |          |

| 62     | 46                          |       | PA5      | PIA5     | ADC5     |          |          |          |

| 63     | 47                          | 10    | PB5      | PIB5     | ADC13    |          |          |          |

| 64     | 48                          |       | PA6      | PIA6     | ADC6     |          |          |          |

BF7006AMXX series supports ARM SW two-wire debugging protocol, and provides complete upper and lower computers, connectors and simulation tools. Among them, SWDAT (the debugging data port) and RESETN (the chip external reset function port) are multiplexed for the same pin, which defaults to the RESETN function. When the chip is connected to the debugging tool, the system will automatically recognize and switch the pin to the SWDAT function. When the chip needs to restore the RESETN function, it needs to be powered on again.

The SCI1 module is mapped to 3 connect, and only one can be selected at the same time.

Datasheet Page 17 of 161

# 2.3 Pin function description

| Category     | Signal         | Signal function description                                                                    |

|--------------|----------------|------------------------------------------------------------------------------------------------|

|              | IOVCC          | IO power supply                                                                                |

|              | IOVSS          | IO power ground                                                                                |

| D            | VDD            | Power supply                                                                                   |

| Power pin    | VSS            | Power ground                                                                                   |

|              | VREFA          | ADC reference power supply                                                                     |

|              | VREFS          | ADC reference power ground                                                                     |

|              | RESETn/SWDAT   | Reset input/debug data port (default internal pull-up)                                         |

|              | NMI            | External Advanced Interrupt                                                                    |

|              | SWCLK          | Debug port (default internal pull-up)                                                          |

|              | OLKOUT         | Clock output, which can output external crystal clock divided by 8,internal 250KHz clock (1MHz |

| System pin   | CLKOUT         | divided), internal 32KHz (128KHz divided) clock and PLL clock divided by 16                    |

|              | CLKOUTS        | Clock output 2, which can output external crystal clock divided by 16 and internal 1MHz        |

|              | CLKOUT2        | clock divided by 4                                                                             |

|              | XTAL_IN        | Crystal input                                                                                  |

|              | XTAL_OUT       | Crystal output                                                                                 |

|              | SCI0_RX        | SCI0 (UART/LIN) input                                                                          |

|              | SCI0_TX        | SCI0 (UART/LIN) output                                                                         |

| Communicati  | SCI1_RX        | SCI1 (UART/LIN) input                                                                          |

| on Interface | SCI1_TX        | SCI1 (UART/LIN) output                                                                         |

|              | CAN_RX         | CAN receive data                                                                               |

|              | CAN_TX         | CAN transmit data                                                                              |

|              | PWM_CH0        | Advanced counter channel 0                                                                     |

|              | PWM _CH1       | Advanced counter channel 1                                                                     |

|              | PWM _CH2       | Advanced counter channel 2                                                                     |

| Counter      | PWM _CH3       | Advanced counter channel 3                                                                     |

|              | PWM _CH4       | Advanced counter channel 4                                                                     |

|              | PWM _CH5       | Advanced counter channel 5                                                                     |

|              | PWM _CLK_IN    | Advanced counter external count clock                                                          |

| ADC          | ADC0~ADC23     | 24 channels of ADC                                                                             |

| CDIO         | PAx~PGx        | General input/output                                                                           |

| GPIO         | PIAx、PIBx、PIDx | External interrupt                                                                             |

|              | •              |                                                                                                |

Datasheet Page 18 of 161

# 3 System

BF7006AMXX is a 32-bit Cortex\_M0 core MCU, its design architecture is based on AMBA AHB2.0 bus integration, which simplifies the system to a certain extent. The system mainly includes system functional components such as Cortex\_M0 CPU, clock management unit, reset management unit, power management unit, interrupt management unit, functional safety management unit, etc.

#### 3.1 CPU

The CPU is a standard 32-bit Cortex\_M0, please refer to the ARM Cortex\_M0 user manual for details, including the internal timer (System Tick), which is not repeated here.

## 3.2 Address map

The start address and end address of each module device of BF7006AMXX are allocated as follows:

|    | Device name               | Start address | End address |

|----|---------------------------|---------------|-------------|

| 1  | FLASH main program memory | 0x0000_0000   | 0x0001_7FFF |

| 2  | FLASH_NVR memory          | 0x0001_8000   | 0x0001_8FFF |

| 3  | SRAM memory               | 0x2000_0000   | 0x2000_0FFF |

| 4  | EEPROM flash              | 0x4000_0000   | 0x4000_07FF |

| 5  | EEPROM_NVR memory         | 0x4000_0800   | 0x4000_08FF |

| 6  | FLASH/EEPROM controller   | 0x5000_0000   | 0x5000_FFFF |

| 7  | System controller         | 0x5001_0000   | 0x5001_FFFF |

| 8  | SCI0/1                    | 0x5004_0000   | 0x5004_FFFF |

| 9  | CAN                       | 0x5005_0000   | 0x5005_FFFF |

| 10 | PWM                       | 0x5006_0000   | 0x5006_FFFF |

Datasheet Page 19 of 161

| 11 | RTC            | 0x5007_0000 | 0x5007_FFFF |

|----|----------------|-------------|-------------|

| 12 | WDT            | 0x5008_0000 | 0x5008_FFFF |

| 13 | ADC controller | 0x5009_0000 | 0x5009_FFFF |

| 14 | GPIO           | 0x500A_0000 | 0x500A_FFFF |

| 15 | TIMER0/1       | 0x500B_0000 | 0x500B_FFFF |

### 3.3 System management

The BF7006AMXX system contains four parts: interrupt management, clock and power consumption management, reset management and safety management. Each part can be configured to realize various control functions and management of the system in order to provide different application needs.

#### 3.3.1 Interrupt management

BF7006AMXX interrupt is based on Cortex\_M0 interrupt control, and the corresponding function extension is added externally. The main features are:

- 1. Each module peripheral corresponds to an independent interrupt source;

- 2. A total of 24 external interrupts are available, of which 24 interrupts on A, B, and D ports are multiplexed with 1 interrupt source and distinguished by interrupt flag bits;

- 3. The system interrupt SYS\_INTR has 9 interrupts, which are crystal startup initialization error, crystal detection error, FLASH\_NVR check error, FLASH protection error operation, EEPROM protection error operation, FLASH ECC 1 bit error, FLASH ECC 2 bit error, EEPROM ECC 1 bit error, EEPROM ECC 2 bit error, each interrupt has a corresponding interrupt flag signal;

- 4. Support LVDT low voltage step-up and step-down interrupt;

- 5. Support NMI non-maskable interrupt;

- 6. Interrupt priority can be configured;

- 7. Interrupt can be enabled or masked;

### 3.3.1.1 Interrupt allocation

Cortex\_M0 internal exceptions and interrupts are not repeated here, the system interrupt numbers are allocated as follows, to ensure that the program is written corresponding to the correct interrupt number:

| CPU interrupt list | Allocation                | Corresponding status register bit |

|--------------------|---------------------------|-----------------------------------|

| IRQ0               |                           |                                   |

|                    |                           | SYS_INTEN_ETER                    |

|                    |                           | SYS_INTEN_EOER                    |

|                    |                           | SYS_INTEN_FTER                    |

|                    | SYS_INTR system interrupt | SYS_INTEN_FOER                    |

| IRQ1               |                           | SYS_INTEN_EPOT                    |

|                    |                           | SYS_INTEN_FPOT                    |

|                    |                           | SYS_INTEN_ADJ                     |

|                    |                           | SYS_INTEN_XTALCHK                 |

|                    |                           | SYS_INTEN_XTALINIT                |

Datasheet Page 20 of 161

| IRQ2  |                         |                                       |

|-------|-------------------------|---------------------------------------|

| IRQ3  |                         |                                       |

| IRQ4  | LVDT interrupt          | SYS_LVDT_IE_H                         |

| IRQ4  | LVDT interrupt          | SYS_LVDT_IE_L                         |

| IRQ5  | PWM_CH0 interrupt       | PWM_C0SC_IF                           |

| IRQ6  | PWM_CH1 interrupt       | PWM_C1SC_IF                           |

| IRQ7  | PWM_CH2 interrupt       | PWM_C2SC_IF                           |

| IRQ8  | PWM_CH3 interrupt       | PWM_C3SC_IF                           |

| IRQ9  | PWM_CH4 interrupt       | PWM_C4SC_IF                           |

| IRQ10 | PWM_CH5 interrupt       | PWM_C5SC_IF                           |

| IRQ11 | PWM overflow interrupt  | PWM_SC_TOF                            |

| IRQ12 |                         |                                       |

| IRQ13 |                         |                                       |

| IRQ14 |                         |                                       |

| IRQ15 |                         |                                       |

|       |                         | SCI_S1_RX_OVERFLOW_FLAG               |

| IRQ16 | SCI0 ERR interrupt      | SCI_S1_NOSIE_ERR_FLAG                 |

|       |                         | SCI_S1_RX_FULL_FLAG                   |

| IRQ17 | SCI0 RX interrupt       | SCI_S2_BREAK_CHECK_FLAG               |

|       |                         | SCI_S2_RX_EDGE_FLAG                   |

|       |                         | SCI_S1_TX_EMPTY_FLAG                  |

| IRQ18 | SCI0 TX interrupt       | SCI_S1_TX_COMP_FLAG                   |

| 10010 | 001/500                 | SCI_S1_RX_OVERFLOW_FLAG               |

| IRQ19 | SCI1 ERR interrupt      | SCI_S1_NOSIE_ERR_FLAG                 |

|       |                         | SCI_S1_RX_FULL_FLAG                   |

| IRQ20 | SCI1 RX interrupt       | SCI_S2_BREAK_CHECK_FLAG               |

|       |                         | SCI_S2_RX_EDGE_FLAG                   |

| IDOM  | COM TV into annual      | SCI_S1_TX_EMPTY_FLAG                  |

| IRQ21 | SCI1 TX interrupt       | SCI_S1_TX_COMP_FLAG                   |

|       |                         | GPIO_PTSC_IF                          |

| IRQ22 | CDIO ovternel interrunt | GPIO_INTST (GPIOA)                    |

| IRQ22 | GPIO external interrupt | GPIO_INTST (GPIOB)                    |

|       |                         | GPIO_INTST (GPIOD)                    |

| IRQ23 | ADC interrupt           | ADC_SC1_COCO                          |

| IRQ24 |                         |                                       |

| IRQ25 | RTC interrupt           | RTC_SC_IF                             |

|       |                         | CAN_CLRISR_WUPI                       |

| IRQ26 | CAN WAKEUP interrupt    | CAN_IF_WUPI                           |

|       |                         | SYS_CAN_SPWKFLAG                      |

|       |                         | CAN_IF_BEI                            |

| IRQ27 | Z CAN EDD interment     | CAN_IF_ALI                            |

| IRQ21 | CAN ERR interrupt       | CAN_IF_EPI                            |

|       |                         | CAN_IF_DOI                            |

|       |                         | · · · · · · · · · · · · · · · · · · · |

Datasheet Page 21 of 161

|       |                  | CAN_IF_EI      |

|-------|------------------|----------------|

|       |                  | CAN_CLRISR_BEI |

|       |                  | CAN_CLRISR_ALI |

|       |                  | CAN_CLRISR_EPI |

|       |                  | CAN_CLRISR_DOI |

|       |                  | CAN_CLRISR_EI  |

| IRQ28 | CAN RX interrupt | CAN_IF_RI      |

| IRQ29 | CAN TX interrupt | CAN_IF_TI      |

| INQ29 | CAN 1X Interrupt | CAN_CLRISR_TI  |

| IRQ30 | Timer0 interrupt | TIMER_CFG_IF   |

| IRQ31 | Timer1 interrupt | TIMER_CFG_IF   |

#### 3.3.1.2 Interrupt enable and priority

The interrupt enable signal is divided into two types:

- 1. The processor CPU has its own enable register (ISER), which is used to control whether the interrupt signal sent to the CPU is valid;

- 2. The work mode enable register, based on the application configuration, sends external interrupt and internally generated interrupt to the CPU;

- 3. The external NMI interrupt signal can be sent to CPU according to the working status;

- 4. About the configuration of interrupt priority, eight 32-bit registers can be configured in CPU, and each interrupt has an 8-bit register to select the priority configuration value, the default interrupt priority is 0 to 31. Please refer to the ARM Cortex M0 user manual for details, which is not repeated here.

### 3.3.1.3 Interrupt wakeup

In the system low-power mode, turning off the clock and some other analog modules can save power consumption. At the sametime, the system can be waked up by LVDT interrupt. NMI interrupt. all external interrupt. can interrupt. SCI0/1 interrupt. RTC interrupt. WDT reset in low-power mode. All wakeup interrupts are asynchronous wakeup. According to the different low-power modes of the system and the choice of clock source, the wakeup process and the required time are different. For more details, please refer to the clock and power management chapter.

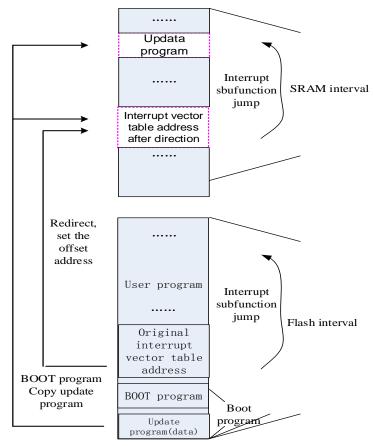

## 3.3.1.4 Interrupt vector redirection and online upgrade

BF7006AMXX supports the system vector redirection function. After updating the user program, the system can map the interrupt list address to the latest user program and execute the interrupt service function of the user program.

BF7006AMXX provides two online upgrade methods:

Datasheet Page 22 of 161

- 1. Run BOOT program loading program to update data, in the process of writing to the chip, CPU is automatically in a pause state, until the user program update data is successfully written in the FLASH. loop in this way:

- 2. The vector redirection function can also be used for online upgrade and providing application development BOOT.

During the online upgrade process, the user programs stored in FLASH except for the BOOT program, the user's function program and interrupt service program need to be updated and overwritten. Therefore, during the online upgrade process, if interrupt is needed (online upgrade by CAN and CAN interrupts are needed), the interrupt vector table and interrupt service routine need to be redirected. Since FLASH needs to be updated and cannot be read and written at the same time, it is generally directed(mapped) to SRAM. For the same reason, since the upgrade program cannot be read and executed by the CPU at the same time when the FLASH is being updated, the upgrade program also needs to be copied to RAM for execution. The BOOT program consists of a boot program and an upgrade program, and the upgrade program includes an interrupt vector table and an interrupt service function. Since the upgrade program cannot be executed in FLASH, the upgrade program in FLASH can be regarded as the data to be moved by the boot program. Therefore, it can be called an upgrade program only when it is moved to SRAM and executed.

Process guidance for BOOT program operation:

- 1. After the CPU is reset, BOOT program starts to run;

- 2. If there is no upgrade requirement, jump to the user function program. If there is an upgrade requirement, start to execute the BOOT program;

- 3. Update the user program according to different online upgrade methods;

Datasheet Page 23 of 161

The offset address of the interrupt vector table must be configured before the upgrade program starts the interrupt. Through two sets of 32-bit original address registers and two sets of 32-bit mapped address registers, the range of the interrupt vector table and the range of the mapped interrupt vector table are configured. When the CPU access address falls in the address range of the original interrupt vector table, it is mapped to the mapped address range through the mapping logic, so that the interrupt response can be performed correctly.

#### 3.3.2 Reset management

BF7006AMXX uses a variety of reset sources to reset the chip system, and different reset sources enter different reset states, which are mainly divided into two types: power-on reset and functional global reset. After the power-on initialization reset, all units and registers of the chip are reset. And other functional resets can reset all functional units except for the key configuration and status registers of the system. Features:

- 1. Support multiple reset sources;

- 2. Asynchronous reset and synchronous release to ensure reliability;

- 3. Each reset source has a corresponding reset state flag;

- 4. External reset supports reset signal filtering function;

#### 3.3.2.1 Reset source

- 1. Power-on reset: After the system is powered on, the analog module sends a reset signal to reset all units:

- 2. Power-down reset: When the power-down reset module is enabled, the system is powered down. And when the voltage reaches the reset threshold, all units are reset;

- 3. Watchdog reset: A reset signal is generated after the watchdog timer overflows to reset the system;

- 4. Software reset: Reset the system by writing the software reset register in the CPU;

- 5. CPU crash reset: The CPU program is disordered to make the internal LOCKUP signal enable, and the system is reset;

- 6. External pin reset: reset the system by pulling down the external reset function pin, the reset can be filtered to prevent false reset caused by external interference;

- 7. Address overflow reset: The FLASH address exceeds the normal range when the CPU executes the addressing instruction, and the system resets when the address overflow occurs;

- 8. Oscillator clock start-up failure reset: external crystal oscillator start-up failure (this function is usually used when the chip uses an external crystal oscillator as the system clock);

- Oscillator clock failure reset: When the system clock failure monitoring unit detects the failure of the

external crystal oscillator, the system is reset (this function is usually used when the chip uses an

external crystal oscillator as the system clock);

Datasheet Page 24 of 161

#### 3.3.2.2 Reset filter

For the external reset function, in order to avoid interference signals from causing the chip system to enter the reset state, the system supports the filtering function of the external reset signal, and the filtering clock is RC32KHz.

When the external port reset function is enable and the external reset filter function is required, the RC32K clock source needs to be ensured in working state and the register SYS\_EXFLT=1. The filter time is a valid RC\_32KHz clock, and the filter time is 30us~60us. If the RC32KHz clock source is not turned on and the configuration filter function is enabled, the external reset function will be invalid and the reset source cannot be sent to the system, this condition needs to pay attention.

For other resets, an asynchronous reset is designed inside the chip, and the registers are released synchronously to ensure that the reset signal is reliable and effective.

Datasheet Page 25 of 161

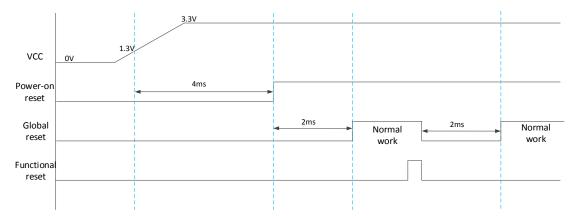

#### 3.3.2.3 Reset sequence

- 1. The chip is powered on, VCC reaches 1.3V, and the power-on reset signal is valid for 4ms;

- 2. After that, the system starts to perform a global reset. After 2ms, the chip global reset is completed and the system starts to work normally;

- 3. When other functions (power failure, watchdog, address overflow, soft reset, CPU crash, crystal oscillator start-up failure, crystal oscillator failure, external pin) reset during operation, a valid system reset occurs and a global reset occurs. After 2ms, the chip global reset is completed and the system starts to work normally.

Note that the VCC power-on time from 0V to 3.3V needs to be completed within 4ms.

## 3.3.3 Clock and power consumption management

BF7006AMXX supports multiple clock sources, and the system working clock supports multiple frequency divisions. Each peripheral module supports separate control of the clock for better control power consumption and improving system efficiency. At the same time, the system supports two low-power modes to reduce system operating current as much as possible, and supports multiple functional wake-up mechanisms.

Datasheet Page 26 of 161

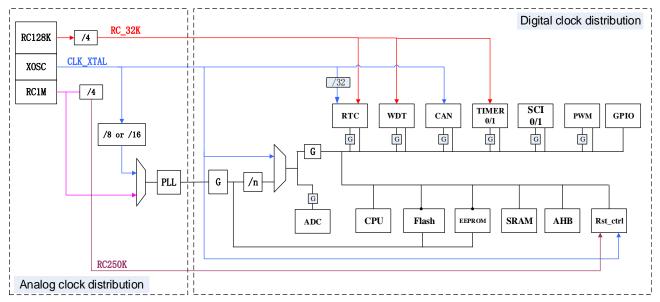

#### 3.3.3.1 Clock architecture

Clock structure description:

- The system contains 3 analog clock sources: RC128KHz, RC1MHz and external crystal oscillator. RC128KHz is divided by 4 on the analog side to form an RC32KHz clock source and sent to the digital system; among them, RC1MHz is divided by 4 on the analog side to form a RC250KHz clock source for using in digital systems; And external crystal oscillators typically support 8MHz and 16MHz;

- The analog PLL phase-locked loop access clock source supports internal RC1MHz and external

crystal oscillator clock, but the access clock only supports 1MHz. Therefore, when the PLL access

clock source selects the external crystal oscillator, it must be divided by 8 or 16 to 1MHZ according to

the different external crystal frequency.

- 3. The system clock is the internal PLL output clock; the maximum PLL output clock frequency is 32MHz, and SYS\_CLK\_SEL can be configured for frequency division according to different application requirements; when the external crystal oscillator clock is selected as the system clock or the crystal oscillator clock is used as the PLL access clock source. When waking up from power consumption, due to the influence of the crystal oscillator start-up time, the waiting time of the system will be much longer than the case of selecting the internal RC1MHz as the PLL access clock source and as the system clock;

- 4. The CAN module working clock supports external crystal oscillator and internal system clock. Through program configuration, it should be noted that when the crystal oscillator is selected as the working clock, there is a cross-time domain problem with the system running clock. The SYS\_CAN\_DOMAIN register needs to be properly configured; When the module clock is not supplied to the CAN module, any register of the CAN module cannot be accessed, and the access action may cause the system to fault;

- 5. The WDT count clock can be selected by sofeware including RC32KHz and its 32 frequency division;

- 6. RTC count clock can be selected by software including RC32KHz, its 32 frequency division and 32 frequency division of external crystal oscillator;

- 7. All peripherals and system clocks can be gated to reduce power consumption;

Datasheet Page 27 of 161

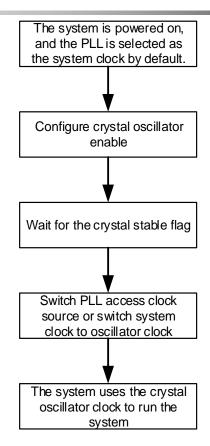

#### 3.3.3.2 Clock selection and switch

By default, the system selects the internal RC1MHz clock as the access clock source of the PLL, and the PLL output frequency divided by 2 (16MHz) is used as the system clock. The external crystal oscillator is turned off by default. Therefore, the working clock before system power-on initialization is based on the internal RC1MHz clock.

If the system requires a high-precision clock source in a certain application, you can configure to turn on the crystal clock and switch the system clock to an external crystal clock source in the initialization program, or switch the PLL access clock source to an external crystal clock. Note that since the crystal oscillator needs a certain stabilization time to turn on and successfully start-up, it is necessary to ensure that the crystal oscillator clock is in a stable state before the software configuration is switched, otherwise the system will fail.

Similarly, if the external crystal oscillator clock is turned off to reduce power consumption when the system enters the low-power sleep mode, and the system working clock is based on the external crystal oscillator clock, the wake-up time will include the crystal oscillator start-up stabilization time and have long wake-up time (please refer to the electrical characteristics of crystal oscillator stabilization time for details).

#### 3.3.3.3 Working modes

BF7006AMXX has 4 working modes, which can be selected according to different situations:

- 1. Active mode: The module keeps working normally, and the function of each module is controlled by the software configuration;

- 2. Sleeping mode: The CPU and system modules stop working, and the functions of other peripheral modules are controlled by software configuration and support interrupt wake-up;

- 3. Sleepdeep mode: In this mode, all digital modules stop working, and some analog modules work selectively (configured according to specific wake-up conditions), and support condition-triggered wake-up;

- 4. Debug mode: Used for testing, debugging, and programming. Enter directly through the external ARM SW debug interface;

Different working modes control the clock source:

| Work mode | Conditions for accessing mode                | State of clock source |                        |

|-----------|----------------------------------------------|-----------------------|------------------------|

|           |                                              | XTAL                  | Configured by software |

| Action    |                                              | RC128K                | Configured by software |

| Active    |                                              | RC1MHz                | Work                   |

|           |                                              | PLL                   | work                   |

|           |                                              | XTAL                  | Configured by software |

| C1 .      | Configure CPU sleep mode as normal sleep and | RC128K                | Configured by software |

| Sleeping  | execute WFI instruction                      | RC1MHz                | work                   |

|           |                                              | PLL                   | work                   |

Datasheet Page 28 of 161

# BF7006AMXX

|           |                                            | XTAL   | Configured by software |

|-----------|--------------------------------------------|--------|------------------------|

| Cleandean | Configure CPU sleep mode as deep sleep and | RC128K | Configured by software |

| Sleepdeep | execute WFI instruction                    | RC1MHz | close                  |

|           |                                            | PLL    | close                  |

|           | External interface input                   | XTAL   | Configured by software |

| Dohum     |                                            | RC128K | Configured by software |

| Debug     |                                            | RC1MHz | work                   |

|           |                                            | PLL    | work                   |

Different working modes control the various modules of the system:

| Module   | Active           | Sleeping         | Sleepdeep        |

|----------|------------------|------------------|------------------|

| CPU      | Work             | PD               | PD               |

| AHB      | Work             | PD               | PD               |

| FLASH    | Work             | PD               | PD               |

| EEPROM   | Work             | PD               | PD               |

| SRAM     | Work             | PD               | PD               |

| SYS_CTRL | Work             | PD               | PD               |

| TIMERO/1 | Software control | Software control | PD               |

| PWM      | Software control | Software control | PD               |

| RTC      | Software control | Software control | Software control |

| WDT      | Software control | Software control | Software control |

| CAN      | Software control | Software control | PD               |

| SCI0/1   | Software control | Software control | PD               |

| GPI0     | Software control | Software control | PD               |

| ADC      | Software control | Software control | Software control |

| LVDT     | Software control | Software control | Software control |

| BOR      | Software control | Software control | Software control |

Datasheet Page 29 of 161

#### 3.3.3.4 Low-power wakeup

- Idle mode wake-up: Any peripheral interrupt, watchdog reset and external reset can wake up the system. Interrupt wake-up will make the system continue to run from the last sleep point, reset wakeup will reset the system from idle mode and restart operation;

- Sleep mode wake-up: External interrupts (including NMI), RTC interrupts, LVDT low-voltage interrupts, CAN interrupts, SCI interrupts, watchdog resets and external resets can wake up the system. Interrupt wake-up will make the system continue to run from the last sleep point. Reset wake-up makes the system reset from idle mode and restart operation;

- 3. CAN wake-up in sleep mode: support external CAN communication dominant level wake-up, and can choose whether to filter (for details, see the chapter waking up the system through CAN);

- 4. SCI wake-up in sleep mode: support external SCI communication pin pulse wake-up (see the SCI interrupt wake-up chapter for details);

- 5. ADC wake-up in sleep mode: see the ADC sleep wake-up chapter for details;

Note: Since the sleep mode system shuts down most of the analog modules and all digital modules, when waking up, the system first needs to ensure that the power supply and clock are stable before waking up the CPU and digital system normally. Therefore, it takes a long time to wake up, including the power supply stabilization time 60us, PLL stabilization time 200us~500us (software configurable) and external crystal oscillator stabilization time (if the system uses crystal oscillator as the system working clock, 4096 or 8192 software-selectable crystal oscillator stabilization period and crystal oscillator start-up stabilization time are required).

### 3.3.3.5 Oscillator clock initialization procedure

BF7006AMXX supports the external oscillator clock directly as the system running clock, or the oscillator clock as the PLL access clock source, and then uses the PLL clock as the system clock, which has reached higher application accuracy requirements. When the external crystal oscillator is directly used as the system operating clock, the maximum frequency does not exceed 16MHz; when the oscillator clock is used as the PLL access clock source, and then the PLL clock is used as the system clock, the maximum frequency of the system does not exceed 32MHz. Before the system initialization program switches the crystal oscillator clock, ensure that the crystal oscillator starts to oscillate stably.

Datasheet Page 30 of 161

#### 3.3.4 Functional safety management

In order to better make the system meet the ASILB safety level, BF7006AMXX supports a variety of functional safety management mechanisms to realize the safety protection of logic functions from the hardware level.

### 3.3.4.1 External oscillator failure monitoring

There are two situations for monitoring the failure of the external crystal oscillator:

1. Crystal oscillator initialization start-up failure monitoring:

After this function is enabled, when the crystal oscillator initialization is started, the internal RC1MHz 4 divider clock RC250KHz will automatically time for 100ms. After 100ms, the crystal oscillator startup success flag will be monitored. If the correct crystal oscillator startup success flag is monitored, the crystal oscillator has been successfully started and the system can continue to run; if the correct crystal oscillator startup success flag is not monitored, the corresponding error interrupt will be issued and the system will be reset according to the register SYS\_XTAL\_INIT configuration (reset is typically used when the crystal oscillator is used as the system clock source);

2. Failure monitoring when crystal oscillator is working;

When the crystal oscillator is working normally, there is a risk of failure. When this function is enabled, the system uses the internal RC1MHz divide-by-4 clock RC250KHz to monitor the crystal oscillator clock, which means that the crystal oscillator clock (fast clock) is used to count 2 cycles of RC250KHz (slow clock). Considering the deviation characteristics of the clock by the environment, the monitoring function sets a reasonable count value within a certain interval (register SYS\_XTAL\_CHKCNT configuration). When the count value is within this interval, the crystal oscillator

Datasheet Page 31 of 161

is considered normal; when the count value exceeds the counting interval, the crystal oscillator is considered to has an error and an error interrupt is issued; when this error occurs 8 times or more, whether to reset the system according to the SYS\_XTAL\_CHK configuration (reset is typically used when the crystal oscillator is used as the system clock source).

When the crystal oscillator module is not enabled, the monitoring function will be unavailable. The application should be aware that this function will not work normally when the crystal oscillator is turned off or the system enters the sleep mode.

#### 3.3.4.2 Low-Voltage and power down monitoring

BF7006AMXX supports system power supply monitoring, including low-voltage monitoring LVDT and power-down monitoring BOR. The system provides three low-voltage points of 4.5V, 4.0V and 3.5V, and a power-down reset point of 3.1V. When the system power supply voltage is less than the above value, in order to ensure the safety of the system, the system will issue a low-voltage interrupt or directly reset the system.

LVDT provides two interrupt flag bits, namely the low-voltage interrupt flag and the recovery interrupt flag, which can better indicate the current voltage status. However, only low-voltage interrupts can wake the system from sleep mode.

#### 3.3.4.3 Memory protection and check

The FLASH and EEPROM of BF7006AMXX support erasing and writing protection to prevent the program, especially the BOOT program, from erasing by mistake. The size of the protection space is controlled by the configuration of the corresponding registers FLASH\_LOCK\_SIZE and EEPROM\_LOCK\_SIZE, and the configuration of this register requires EFLASH\_UNLOCK to be unlocked before the protection is unlocked.

When the chip is connected to the debugging function, the protection function is automatically unlocked.

At the same time, FLASH and EEPROM provide a 32-bit + 6-bit ECC check mechanism, which can correct 1-bit or 2-bit error detection, which improves the reliability of the memory at the system level.

#### FLASH address protection:

| FLASH_LOCK_SIZE | Address protection range | Size (Kbytes) |

|-----------------|--------------------------|---------------|

| 0x00            | Flash_NVR                | 0             |

| 0x01            | Flash_NVR + 2K           | 2             |

| 0x02            | Flash_NVR + 4K           | 4             |

| 0x03            | Flash_NVR + 6K           | 6             |

|                 |                          |               |

| 0x30            | Flash_NVR + 96K          | 96            |

Datasheet Page 32 of 161

EEPROM address protection:

| EEPROM_LOCK_SIZE | Address protection range | Size (bytes) |

|------------------|--------------------------|--------------|

| 0x00             | unprotected              | 0            |

| 0x01             | EEP_NVR + 64Bytes        | 64           |

| 0x02             | EEP _NVR + 128Bytes      | 128          |

| 0x03             | EEP _NVR + 196Bytes      | 196          |

|                  |                          |              |

| 0x20             | EEP _NVR + 2048Bytes     | 2048         |

#### 3.3.4.4 Functional safety reset

BF7006AMXX supports multiple functional safety resets, including program address access overflow reset, CPU locked protection reset, and hardware watchdog reset.

- 1. Program address access overflow reset: When the program instruction access exceeds the limited address range, the system will consider this operation illegal and will issue an address overflow reset to prevent the program from running away;

- 2. CPU locked protection reset: reset based on Cortex\_M0's own functional signal LOCKUP design;

- 3. Hardware watchdog reset: When the program does not clear the watchdog timer within the specified time, the system is considered to be in an infinite loop or paralyzed state. At this time, the hardware watchdog issues a system reset directly; the system uses an independent watchdog count clock to avoid system disorder to affect the watchdog operation.

#### 3.3.4.5 ADC temperature detection channel

BF7006AMXX contains 1 internal channel, which supports the detection of chip temperature changes. The ADC conversion data fed back by this channel is different at different temperatures Users can evaluate the current chip temperature based on the quasi-linear relationship between this data and temperature to ensure system safety. See the ADC chapter for specific configuration.

## 3.3.5 Register map

System controller module address range: 0x5001\_0000~0x5001\_FFFF

| Address<br>offset | Register name      | R/W | Functional description            | Initial value |

|-------------------|--------------------|-----|-----------------------------------|---------------|

| 0x00              | SYS_PTSEL          | R/W | Port function seclection register | 0x00          |

| 0x04              | SYS_XTAL_CTRL      | R/W | Xtal control register             | 0x00          |

| 0x08              | SYS_PLL_SOURCE_SEL | R/W | Pll source clock select register  | 0xACB3        |

| 0x0C              | SYS_CLK_SEL        | R/W | System clock select register      | 0x3CA2        |

Datasheet Page 33 of 161

| 0x10  | SYS_VECTOR_OFFSET | R/W | Vector redirection offset register                 | 0x0000_0000 |

|-------|-------------------|-----|----------------------------------------------------|-------------|

| 0x14  | SYS_CLK_PD        | R/W | Analog work enable register                        | 0x06        |

| 0x18  | SYS_CAN_DOMAIN    | R/W | CAN time domain counting time register             | 0x04        |

| 0x1C  | SYS_CLK_OUT       | R/W | Analog clock output register                       | 0x0000      |

| 0x20  | SYS_IO_LOCK       | R/W | IO function lock register                          | 0x01        |

| 0x24  | SYS_LVDT_CRL      | R/W | Voltage monitoring register                        | 0x07        |

| 0x28  | SYS_EXRST         | R/W | External reset function enable register            | 0x01        |

| 0x2C  | SYS_EXFLT         | R/W | External reset filter register                     | 0x01        |

| 0x34  | SYS_PERH_HALT     | R/W | Debug count stop control register                  | 0x01        |

| 0x38  | SYS_PLL_T         | R/W | PLL stabilization time set register                | 0x00        |

| 0x40  | SYS_CAN_CLKSEL    | R/W | CAN clock select register                          | 0x00        |

| 0x44  | SYS_CAN_RST       | R/W | CAN module reset register                          | 0x01        |

| 0x48  | SYS_CAN_SPWKFLAG  | R/W | System wakeup CAN flag register                    | 0x00        |

| 0x100 | SYS_RSTSTAT       | R/W | Reset status register                              | 0x0001      |

| 0x104 | SYS_INTEN         | R/W | System interrupt enable register                   | 0x0000      |

| 0x108 | SYS_INTFLG        | R/W | System interrupt status register                   | 0x0000      |

| 0x10C | SYS_XTAL_CHK      | R/W | Xtal work detection failure register               | 0x00        |

| 0x110 | SYS_XTAL_CHKCNT   | R/W | Xtal work failure monitoring interval set register | 0x0002_0008 |

| 0x114 | SYS_XTAL_INIT     | R/W | Xtal initialization failure monitoring register    | 0x00        |

| 0x118 | SYS_LVDT_IE       | R/W | 1VDT interrupt enable register                     | 0x00        |

| 0x11C | SYS_LVDT_IF       | R/W | 1VDT interrupt flag register                       | 0x00        |

# 3.3.6 Register description

# 3.3.6.1 SYS\_PTSEL register

| Address | Bit | Name      | R/W | Reset | Description                                                                                                                                                                                                                                     |

|---------|-----|-----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |     |           |     | value |                                                                                                                                                                                                                                                 |